|

|

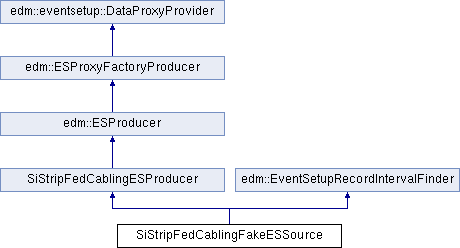

Builds cabling map based on list of DetIds and FedIds read from ascii files. More...

#include <SiStripFedCablingFakeESSource.h>

Public Member Functions | |

| SiStripFedCablingFakeESSource (const edm::ParameterSet &) | |

| ~SiStripFedCablingFakeESSource () | |

Protected Member Functions | |

| virtual void | setIntervalFor (const edm::eventsetup::EventSetupRecordKey &, const edm::IOVSyncValue &, edm::ValidityInterval &) |

Private Member Functions | |

| virtual SiStripFedCabling * | make (const SiStripFedCablingRcd &) |

Private Attributes | |

| edm::FileInPath | detIds_ |

| edm::FileInPath | fedIds_ |

| edm::ParameterSet | pset_ |

Builds cabling map based on list of DetIds and FedIds read from ascii files.

Definition at line 17 of file SiStripFedCablingFakeESSource.h.

| SiStripFedCablingFakeESSource::SiStripFedCablingFakeESSource | ( | const edm::ParameterSet & | pset | ) | [explicit] |

Definition at line 18 of file SiStripFedCablingFakeESSource.cc.

: SiStripFedCablingESProducer( pset ), detIds_( pset.getParameter<edm::FileInPath>("DetIdsFile") ), fedIds_( pset.getParameter<edm::FileInPath>("FedIdsFile") ), pset_(pset) { findingRecord<SiStripFedCablingRcd>(); edm::LogVerbatim("FedCabling") << "[SiStripFedCablingFakeESSource::" << __func__ << "]" << " Constructing object..."; }

| SiStripFedCablingFakeESSource::~SiStripFedCablingFakeESSource | ( | ) |

Definition at line 32 of file SiStripFedCablingFakeESSource.cc.

{

edm::LogVerbatim("FedCabling")

<< "[SiStripFedCablingFakeESSource::" << __func__ << "]"

<< " Destructing object...";

}

| SiStripFedCabling * SiStripFedCablingFakeESSource::make | ( | const SiStripFedCablingRcd & | ) | [private, virtual] |

Builds cabling map based on ascii files.

Implements SiStripFedCablingESProducer.

Definition at line 40 of file SiStripFedCablingFakeESSource.cc.

References SiStripFecCabling::addDevices(), SiStripFedCablingESProducer::ccuAddr(), SiStripFedCablingESProducer::ccuChan(), results_mgr::conn, SiStripFecCabling::connections(), SiStripFecCabling::countDevices(), SiStripFecCabling::crates(), detIds_, SiStripFedCablingESProducer::fecCrate(), SiStripFedCablingESProducer::fecRing(), SiStripFedCablingESProducer::fecSlot(), SiStripModule::fedCh(), fedIds_, edm::FileInPath::fullPath(), SiStripDetInfoFileReader::getAllDetIds(), edm::ParameterSet::getParameter(), SiStripKey::key(), LogTrace, sistrip::mlCabling_, NumberOfDevices::print(), and pset_.

{

edm::LogVerbatim("FedCabling")

<< "[SiStripFedCablingFakeESSource::" << __func__ << "]"

<< " Building \"fake\" FED cabling map"

<< " from real DetIds and FedIds (read from ascii file)";

// Create FEC cabling object

SiStripFecCabling* fec_cabling = new SiStripFecCabling();

// Read DetId list from file

SiStripDetInfoFileReader Detreader( detIds_.fullPath() );

typedef std::vector<uint32_t> Dets;

Dets dets = Detreader.getAllDetIds();

// Read FedId list from file

typedef std::vector<uint16_t> Feds;

Feds feds = SiStripFedIdListReader( fedIds_.fullPath() ).fedIds();

bool populateAllFeds=pset_.getParameter<bool>("PopulateAllFeds");

// Iterator through DetInfo objects and populate FEC cabling object

uint32_t imodule = 0;

Dets::const_iterator idet = dets.begin();

Dets::const_iterator jdet = dets.end();

for ( ; idet != jdet; ++idet ) {

uint16_t npairs = Detreader.getNumberOfApvsAndStripLength(*idet).first / 2;

for ( uint16_t ipair = 0; ipair < npairs; ++ipair ) {

uint16_t addr = 0;

if ( npairs == 2 && ipair == 0 ) { addr = 32; }

else if ( npairs == 2 && ipair == 1 ) { addr = 36; }

else if ( npairs == 3 && ipair == 0 ) { addr = 32; }

else if ( npairs == 3 && ipair == 1 ) { addr = 34; }

else if ( npairs == 3 && ipair == 2 ) { addr = 36; }

else {

edm::LogWarning("FedCabling")

<< "[SiStripFedCablingFakeESSource::" << __func__ << "]"

<< " Inconsistent values for nPairs (" << npairs

<< ") and ipair (" << ipair << ")!";

}

uint32_t module_key = SiStripFecKey(fecCrate( imodule ),

fecSlot( imodule ),

fecRing( imodule ),

ccuAddr( imodule ),

ccuChan( imodule )).key();

FedChannelConnection conn( fecCrate( imodule ),

fecSlot( imodule ),

fecRing( imodule ),

ccuAddr( imodule ),

ccuChan( imodule ),

addr, addr+1, // apv i2c addresses

module_key, // dcu id

*idet, // det id

npairs ); // apv pairs

fec_cabling->addDevices( conn );

}

imodule++;

}

// Assign "dummy" FED ids/chans

bool insufficient = false;

Feds::const_iterator ifed = feds.begin();

uint16_t fed_ch = 0;

for ( std::vector<SiStripFecCrate>::const_iterator icrate = fec_cabling->crates().begin(); icrate != fec_cabling->crates().end(); icrate++ ) {

for ( std::vector<SiStripFec>::const_iterator ifec = icrate->fecs().begin(); ifec != icrate->fecs().end(); ifec++ ) {

for ( std::vector<SiStripRing>::const_iterator iring = ifec->rings().begin(); iring != ifec->rings().end(); iring++ ) {

for ( std::vector<SiStripCcu>::const_iterator iccu = iring->ccus().begin(); iccu != iring->ccus().end(); iccu++ ) {

for ( std::vector<SiStripModule>::const_iterator imod = iccu->modules().begin(); imod != iccu->modules().end(); imod++ ) {

if(populateAllFeds){

for ( uint16_t ipair = 0; ipair < imod->nApvPairs(); ipair++ ) {

if ( ifed == feds.end() ) { fed_ch++; ifed = feds.begin(); }

if ( fed_ch == 96 ) {

insufficient = true;

break;

}

std::pair<uint16_t,uint16_t> addr = imod->activeApvPair( imod->lldChannel(ipair) );

SiStripModule::FedChannel fed_channel( (*ifed)/16+1, // 16 FEDs per crate, numbering starts from 1

(*ifed)%16+2, // FED slot starts from 2

*ifed,

fed_ch );

const_cast<SiStripModule&>(*imod).fedCh( addr.first, fed_channel );

ifed++;

}

}else{

// Patch introduced by D.Giordano 2/12/08

//to reproduce the fake cabling used in 2x

//that was designed to fill each fed iteratively

//filling all channels of a fed before going to the next one

if ( 96-fed_ch < imod->nApvPairs() ) { ifed++; fed_ch = 0; } // move to next FED

for ( uint16_t ipair = 0; ipair < imod->nApvPairs(); ipair++ ) {

std::pair<uint16_t,uint16_t> addr = imod->activeApvPair( (*imod).lldChannel(ipair) );

SiStripModule::FedChannel fed_channel( (*ifed)/16+1, // 16 FEDs per crate, numbering starts from 1

(*ifed)%16+2, // FED slot starts from 2

(*ifed),

fed_ch );

const_cast<SiStripModule&>(*imod).fedCh( addr.first, fed_channel );

fed_ch++;

}

}

}

}

}

}

}

if ( insufficient ) {

edm::LogWarning(mlCabling_)

<< "[SiStripFedCablingFakeESSource::" << __func__ << "]"

<< " Insufficient FED channels to cable entire system!";

}

// Some debug

std::stringstream ss;

ss << "[SiStripFedCablingFakeESSource::" << __func__ << "]"

<<" First count devices of FEC cabling " << std::endl;

fec_cabling->countDevices().print(ss);

LogTrace(mlCabling_) << ss.str();

// Build FED cabling using FedChannelConnections

std::vector<FedChannelConnection> conns;

fec_cabling->connections( conns );

SiStripFedCabling* cabling = new SiStripFedCabling( conns );

return cabling;

}

| void SiStripFedCablingFakeESSource::setIntervalFor | ( | const edm::eventsetup::EventSetupRecordKey & | key, |

| const edm::IOVSyncValue & | iov_sync, | ||

| edm::ValidityInterval & | iov_validity | ||

| ) | [protected, virtual] |

Implements edm::EventSetupRecordIntervalFinder.

Definition at line 173 of file SiStripFedCablingFakeESSource.cc.

References edm::IOVSyncValue::beginOfTime(), edm::IOVSyncValue::endOfTime(), and infinity.

{

edm::ValidityInterval infinity( iov_sync.beginOfTime(), iov_sync.endOfTime() );

iov_validity = infinity;

}

Location of ascii file containing DetIds.

Definition at line 36 of file SiStripFedCablingFakeESSource.h.

Referenced by make().

Location of ascii file containing FedIds.

Definition at line 39 of file SiStripFedCablingFakeESSource.h.

Referenced by make().

Definition at line 40 of file SiStripFedCablingFakeESSource.h.

Referenced by make().

1.7.3

1.7.3