|

|

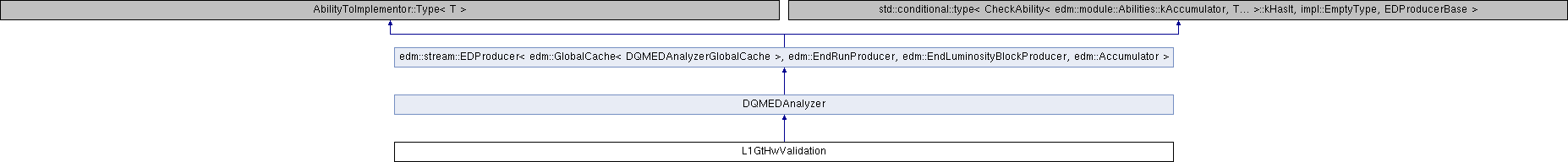

#include <L1GtHwValidation.h>

|

| void | analyze (const edm::Event &, const edm::EventSetup &) override |

| |

| virtual void | compareDaqRecord (const edm::Event &, const edm::EventSetup &) |

| | L1 GT DAQ record comparison. More...

|

| |

| virtual void | compareEvmRecord (const edm::Event &, const edm::EventSetup &) |

| | L1 GT EVM record comparison. More...

|

| |

| virtual void | compareFDL (const edm::Event &, const edm::EventSetup &, const L1GtFdlWord &, const L1GtFdlWord &, const int) |

| | compare the FDL board More...

|

| |

| virtual void | compareGt_Gct (const edm::Event &, const edm::EventSetup &) |

| |

| virtual void | compareGTFE (const edm::Event &, const edm::EventSetup &, const L1GtfeWord &, const L1GtfeWord &, const int) |

| | compare the GTFE board More...

|

| |

| virtual void | comparePSB (const edm::Event &, const edm::EventSetup &, const L1GtPsbWord &, const L1GtPsbWord &) |

| | compare the PSB board More...

|

| |

| virtual void | compareTCS (const edm::Event &, const edm::EventSetup &, const L1TcsWord &, const L1TcsWord &) |

| | compare the TCS board More...

|

| |

| bool | excludedAlgo (const int &) const |

| | exclusion status for algorithm with bit i More...

|

| |

| void | excludedAlgoList () |

| | exclude from comparison some bits with known disagreement - bit list More...

|

| |

| bool | matchCondCategory (const L1GtConditionCategory &, const L1GtConditionCategory &) |

| | book all histograms for the module More...

|

| |

| bool | matchCondL1GtObject (const std::vector< L1GtObject > &, const L1GtObject &) |

| |

| bool | matchCondType (const L1GtConditionType &, const L1GtConditionType &) |

| |

Description: compare hardware records with emulator records for L1 GT records.

Implementation: Get the L1 GT records from data and from emulator.

Compare every board between data and emulator.

- Author

- : Vasile Mihai Ghete - HEPHY Vienna

$Date$

Description: compare hardware records with emulator records for L1 GT records.

Implementation: Get the L1 GT records from data and from emulator.

Compare every board between data and emulator.

- Author

- : Vasile Mihai Ghete - HEPHY Vienna

Definition at line 59 of file L1GtHwValidation.h.

◆ L1GtHwValidation()

Definition at line 52 of file L1GtHwValidation.cc.

68 paramSet.

getParameter<std::vector<edm::ParameterSet> >(

"ExcludeCondCategTypeObject")),

95 if (!(itExclud->getParameter<

std::string>(

"ExcludedCondCategory")).empty()) {

103 if (!(itExclud->getParameter<

std::string>(

"ExcludedCondType")).empty()) {

111 if (!(itExclud->getParameter<

std::string>(

"ExcludedL1GtObject")).empty()) {

References CondNull, edm::ParameterSet::getParameter(), l1GtConditionCategoryStringToEnum(), l1GtConditionTypeStringToEnum(), l1GtObjectStringToEnum(), l1gtPrescaleAlgoToken_, l1gtPrescaleTechToken_, l1gtTrigmaskAlgoToken_, l1gtTrigmaskTechToken_, l1gtTrigmenuToken_, LogDebug, m_excludeCondCategTypeObject, m_excludedCondCategory, m_excludedCondType, m_excludedL1GtObject, m_l1GctDataInputTag, m_l1GtDataDaqInputTag, m_l1GtDataDaqInputToken_, m_l1GtDataEvmInputTag, m_l1GtDataEvmInputToken_, m_l1GtEmulDaqInputTag, m_l1GtEmulDaqInputToken_, m_l1GtEmulEvmInputTag, m_l1GtEmulEvmInputToken_, ObjNull, AlCaHLTBitMon_QueryRunRegistry::string, and TypeNull.

◆ ~L1GtHwValidation()

| L1GtHwValidation::~L1GtHwValidation |

( |

| ) |

|

|

override |

◆ analyze()

◆ bookHistograms()

Implements DQMEDAnalyzer.

Definition at line 151 of file L1GtHwValidation.cc.

174 const char* histName;

176 hName = recString +

"gtfeDataEmul";

177 histName = hName.c_str();

195 int hIndex = (iIndex + 16) % 16;

197 std::stringstream

ss;

199 ss << std::uppercase << std::hex << hIndex;

209 hName = recString +

"FdlDataEmul_" +

str;

210 histName = hName.c_str();

212 std::string hTitle =

"FDL data vs emul mismatch for BxInEvent = " +

str;

234 hName = recString +

"Data_AlgoDecision_" +

str;

235 histName = hName.c_str();

237 hTitle =

"Data: algorithm decision word for BxInEvent = " +

str;

241 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

244 hName = recString +

"Emul_AlgoDecision_" +

str;

245 histName = hName.c_str();

247 hTitle =

"Emul: algorithm decision word for BxInEvent = " +

str;

251 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

255 hName = recString +

"Data_AlgoDecision_Prescaled_" +

str;

256 histName = hName.c_str();

258 hTitle =

"Data: prescaled algorithms: algorithm decision for BxInEvent = " +

str;

262 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

265 hName = recString +

"Emul_AlgoDecision_Prescaled_" +

str;

266 histName = hName.c_str();

268 hTitle =

"Emul: prescaled algorithms: algorithm decision for BxInEvent = " +

str;

272 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

276 hName = recString +

"Data_AlgoDecision_Unprescaled_" +

str;

277 histName = hName.c_str();

279 hTitle =

"Data: unprescaled algorithms: algorithm decision for BxInEvent = " +

str;

283 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

286 hName = recString +

"Emul_AlgoDecision_Unprescaled_" +

str;

287 histName = hName.c_str();

289 hTitle =

"Emul: unprescaled algorithms: algorithm decision for BxInEvent = " +

str;

293 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

297 hName = recString +

"Data_AlgoDecisionAfterMask_" +

str;

298 histName = hName.c_str();

300 hTitle =

"Data, physics partition: algorithm decision word after mask for BxInEvent = " +

str;

304 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

307 hName = recString +

"Emul_AlgoDecisionAfterMask_" +

str;

308 histName = hName.c_str();

310 hTitle =

"Emul, physics partition: algorithm decision word after mask for BxInEvent = " +

str;

314 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

317 hName = recString +

"DataEmul_AlgoDecision_" +

str;

318 histName = hName.c_str();

320 hTitle =

"Data vs emul: non-matching algorithm decision word for BxInEvent = " +

str;

324 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

327 hName = recString +

"DataEmul_AlgoDecision_Prescaled_" +

str;

328 histName = hName.c_str();

330 hTitle =

"Data vs emul: prescaled algorithms with non-matching decision for BxInEvent = " +

str;

334 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

337 hName = recString +

"DataEmul_AlgoDecision_Unprescaled_" +

str;

338 histName = hName.c_str();

340 hTitle =

"Data vs emul: unprescaled algorithms with non-matching decision for BxInEvent = " +

str;

344 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

347 hName = recString +

"DataEmul_AlgoDecision_Unprescaled_Allowed_" +

str;

348 histName = hName.c_str();

350 hTitle =

"Data vs emul: unprescaled algorithms not excluded with non-matching decision for BxInEvent = " +

str;

354 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

357 hName = recString +

"Data_AlgoDecision_NoMatch_" +

str;

358 histName = hName.c_str();

360 hTitle =

"Data: algorithm decision for non-matching cases for BxInEvent = " +

str;

364 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

367 hName = recString +

"Emul_AlgoDecision_NoMatch_" +

str;

368 histName = hName.c_str();

370 hTitle =

"Emul: algorithm decision for non-matching cases for BxInEvent = " +

str;

374 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

377 hName = recString +

"Data_AlgoDecision_Prescaled_NoMatch_" +

str;

378 histName = hName.c_str();

380 hTitle =

"Data: prescaled algorithms: non-matching algorithm decision for BxInEvent = " +

str;

384 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

387 hName = recString +

"Emul_AlgoDecision_Prescaled_NoMatch_" +

str;

388 histName = hName.c_str();

390 hTitle =

"Emul: prescaled algorithms: non-matching algorithm decision for BxInEvent = " +

str;

394 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

397 hName = recString +

"Data_AlgoDecision_Unprescaled_NoMatch_" +

str;

398 histName = hName.c_str();

400 hTitle =

"Data: unprescaled algorithms: non-matching algorithm decision for BxInEvent = " +

str;

404 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

407 hName = recString +

"Emul_AlgoDecision_Unprescaled_NoMatch_" +

str;

408 histName = hName.c_str();

410 hTitle =

"Emul: unprescaled algorithms: non-matching algorithm decision for BxInEvent = " +

str;

414 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

417 hName = recString +

"Data_AlgoDecisionMask_NoMatch_" +

str;

418 histName = hName.c_str();

420 hTitle =

"Data: algorithm decision for non-matching cases after mask for BxInEvent = " +

str;

424 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

427 hName = recString +

"Emul_AlgoDecisionMask_NoMatch_" +

str;

428 histName = hName.c_str();

430 hTitle =

"Emul: algorithm decision for non-matching cases after mask for BxInEvent = " +

str;

434 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

437 hName = recString +

"Data_AlgoDecisionMask_Prescaled_NoMatch_" +

str;

438 histName = hName.c_str();

440 hTitle =

"Data: prescaled algorithms: non-matching algorithm decision after mask for BxInEvent = " +

str;

444 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

447 hName = recString +

"Emul_AlgoDecision_PrescaledMask_NoMatch_" +

str;

448 histName = hName.c_str();

450 hTitle =

"Emul: prescaled algorithms: non-matching algorithm decision after mask for BxInEvent = " +

str;

454 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

457 hName = recString +

"Data_AlgoDecision_UnprescaledMask_NoMatch_" +

str;

458 histName = hName.c_str();

460 hTitle =

"Data: unprescaled algorithms: non-matching algorithm decision after mask for BxInEvent = " +

str;

464 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

467 hName = recString +

"Emul_AlgoDecision_UnprescaledMask_NoMatch_" +

str;

468 histName = hName.c_str();

470 hTitle =

"Emul: unprescaled algorithms: non-matching algorithm decision after mask for BxInEvent = " +

str;

474 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

477 hName = recString +

"DataEmul_AlgoDecisionAfterMask_" +

str;

478 histName = hName.c_str();

481 "Data vs emul, physics partition: non-matching algorithm decision word after mask for BxInEvent = " +

str;

485 ibooker.

book1D(histName,

histTitle, numberAlgoTriggers, 0., numberAlgoTriggers);

489 hName = recString +

"Data_TechDecision_" +

str;

490 histName = hName.c_str();

492 hTitle =

"Data technical trigger decision word for BxInEvent = " +

str;

496 ibooker.

book1D(histName,

histTitle, numberTechTriggers, 0., numberTechTriggers);

499 hName = recString +

"Emul_TechDecision_" +

str;

500 histName = hName.c_str();

502 hTitle =

"Emul: technical trigger decision word for BxInEvent = " +

str;

506 ibooker.

book1D(histName,

histTitle, numberTechTriggers, 0., numberTechTriggers);

509 hName = recString +

"Data_TechDecisionAfterMask_" +

str;

510 histName = hName.c_str();

512 hTitle =

"Data technical trigger decision word after mask for BxInEvent = " +

str;

516 ibooker.

book1D(histName,

histTitle, numberTechTriggers, 0., numberTechTriggers);

519 hName = recString +

"Emul_TechDecisionAfterMask_" +

str;

520 histName = hName.c_str();

522 hTitle =

"Emul: technical trigger decision word after mask for BxInEvent = " +

str;

526 ibooker.

book1D(histName,

histTitle, numberTechTriggers, 0., numberTechTriggers);

529 hName = recString +

"DataEmul_TechDecision_" +

str;

530 histName = hName.c_str();

532 hTitle =

"Data vs emul: non-matching technical trigger decision word for BxInEvent = " +

str;

536 ibooker.

book1D(histName,

histTitle, numberTechTriggers, 0., numberTechTriggers);

538 hName = recString +

"DataEmul_TechDecisionAfterMask_" +

str;

539 histName = hName.c_str();

541 hTitle =

"Data vs emul: non-matching technical trigger decision word after mask for BxInEvent = " +

str;

545 ibooker.

book1D(histName,

histTitle, numberTechTriggers, 0., numberTechTriggers);

555 hName = recString +

"FdlDataEmul_Err";

556 histName = hName.c_str();

559 ibooker.

book1D(histName,

"FDL data vs emul mismatch for non-matching BxInEvent in FDL payload", 13, 0., 13.);

574 hName = recString +

"FdlDataAlgoDecision_Err";

575 histName = hName.c_str();

578 "Data: algorithm trigger decision word, non-matching BxInEvent",

584 hName = recString +

"Emul_AlgoDecision_Err";

585 histName = hName.c_str();

588 "Emul: algorithm trigger decision word, non-matching BxInEvent",

593 hName = recString +

"DataEmul_AlgoDecision_Err";

594 histName = hName.c_str();

598 "Data vs emul: algorithm trigger decision word, non-matching BxInEvent",

604 hName = recString +

"Data_TechDecision_Err";

605 histName = hName.c_str();

608 "Data: technical trigger decision word, non-matching BxInEvent",

613 hName = recString +

"Emul_TechDecision_Err";

614 histName = hName.c_str();

617 "Emul: technical trigger decision word, non-matching BxInEvent",

622 hName = recString +

"DataEmul_TechDecision_Err";

623 histName = hName.c_str();

627 "Data vs emul: technical trigger decision word, non-matching BxInEvent",

637 "Algorithms excluded from data versus emulator agreement flag",

644 m_gtErrorFlag = ibooker.

book1D(

"GTErrorFlag",

"L1 GT error flag for data versus emulator comparison", 5, 0., 5);

677 for (

CItAlgo itAlgo = algorithmMap.begin(); itAlgo != algorithmMap.end(); itAlgo++) {

678 const int algBitNumber = (itAlgo->second).algoBitNumber();

680 std::stringstream

ss;

682 ss << std::uppercase << algBitNumber;

685 const std::string& aName = algBitString +

" " + itAlgo->first;

686 const char* algName = aName.c_str();

689 for (

int iBxInEvent = 0; iBxInEvent <

TotalBxInEvent; ++iBxInEvent) {

692 int hIndex = (iIndex + 16) % 16;

694 std::stringstream

ss;

696 ss << std::uppercase << std::hex << hIndex;

746 if (algBitNumber == *itAlgo) {

References dqm::implementation::IBooker::book1D(), excludedAlgoList(), edm::EventSetup::get(), edm::EventSetup::getData(), L1GtTriggerMenu::gtAlgorithmMap(), L1GtPrescaleFactors::gtPrescaleFactors(), L1GtTriggerMask::gtTriggerMask(), L1GtTriggerMenu::gtTriggerMenuImplementation(), B2GTnPMonitor_cfi::histTitle, l1gtPrescaleAlgoToken_, l1gtPrescaleTechToken_, l1gtTrigmaskAlgoToken_, l1gtTrigmaskTechToken_, l1gtTrigmenuToken_, LogDebug, m_dirName, m_excludedAlgoList, m_excludedAlgorithmsAgreement, m_fdlDataAlgoDecision, m_fdlDataAlgoDecision_Err, m_fdlDataAlgoDecision_NoMatch, m_fdlDataAlgoDecisionMask, m_fdlDataAlgoDecisionMask_NoMatch, m_fdlDataAlgoDecisionPrescaled, m_fdlDataAlgoDecisionPrescaled_NoMatch, m_fdlDataAlgoDecisionPrescaledMask_NoMatch, m_fdlDataAlgoDecisionUnprescaled, m_fdlDataAlgoDecisionUnprescaled_NoMatch, m_fdlDataAlgoDecisionUnprescaledMask_NoMatch, m_fdlDataEmul, m_fdlDataEmul_Err, m_fdlDataEmulAlgoDecision, m_fdlDataEmulAlgoDecision_Err, m_fdlDataEmulAlgoDecisionMask, m_fdlDataEmulAlgoDecisionPrescaled, m_fdlDataEmulAlgoDecisionUnprescaled, m_fdlDataEmulAlgoDecisionUnprescaledAllowed, m_fdlDataEmulTechDecision, m_fdlDataEmulTechDecision_Err, m_fdlDataEmulTechDecisionMask, m_fdlDataTechDecision, m_fdlDataTechDecision_Err, m_fdlDataTechDecisionMask, m_fdlEmulAlgoDecision, m_fdlEmulAlgoDecision_Err, m_fdlEmulAlgoDecision_NoMatch, m_fdlEmulAlgoDecisionMask, m_fdlEmulAlgoDecisionMask_NoMatch, m_fdlEmulAlgoDecisionPrescaled, m_fdlEmulAlgoDecisionPrescaled_NoMatch, m_fdlEmulAlgoDecisionPrescaledMask_NoMatch, m_fdlEmulAlgoDecisionUnprescaled, m_fdlEmulAlgoDecisionUnprescaled_NoMatch, m_fdlEmulAlgoDecisionUnprescaledMask_NoMatch, m_fdlEmulTechDecision, m_fdlEmulTechDecision_Err, m_fdlEmulTechDecisionMask, m_gtErrorFlag, m_gtfeDataEmul, m_l1GtMenu, m_l1GtMenuCacheID, m_l1GtPfAlgo, m_l1GtPfAlgoCacheID, m_l1GtPfTech, m_l1GtPfTechCacheID, m_l1GtTmAlgo, m_l1GtTmAlgoCacheID, m_l1GtTmTech, m_l1GtTmTechCacheID, m_nrEvRun, m_prescaleFactorsAlgoTrig, m_prescaleFactorsTechTrig, m_triggerMaskAlgoTrig, m_triggerMaskTechTrig, NumberOfGtRecords, L1GlobalTriggerReadoutSetup::NumberPhysTriggers, L1GlobalTriggerReadoutSetup::NumberTechnicalTriggers, dqm::impl::MonitorElement::setBinLabel(), dqm::implementation::NavigatorBase::setCurrentFolder(), contentValuesCheck::ss, str, AlCaHLTBitMon_QueryRunRegistry::string, and TotalBxInEvent.

◆ compareDaqRecord()

L1 GT DAQ record comparison.

Definition at line 1798 of file L1GtHwValidation.cc.

1813 bool validData =

false;

1815 if (!gtReadoutRecordData.

isValid()) {

1825 bool validEmul =

false;

1827 if (!gtReadoutRecordEmul.

isValid()) {

1833 if ((!validData) || (!validEmul)) {

1834 edm::LogWarning(

"L1GtHwValidation") <<

"\n No valid product found: DAQ L1GlobalTriggerReadoutRecord"

1835 <<

"\n Data validity [1 = true; 0 = false]: " << validData

1836 <<

"\n Emulator validity: [1 = true; 0 = false]: " << validEmul

1837 <<

"\n DAQ histograms will not be filled.\n"

1850 const std::vector<L1GtFdlWord>& gtFdlVectorData = gtReadoutRecordData->

gtFdlVector();

1851 const std::vector<L1GtFdlWord>& gtFdlVectorEmul = gtReadoutRecordEmul->

gtFdlVector();

1853 int gtFdlVectorDataSize = gtFdlVectorData.size();

1854 int gtFdlVectorEmulSize = gtFdlVectorEmul.size();

1856 if (gtFdlVectorDataSize == gtFdlVectorEmulSize) {

1857 m_myCoutStream <<

"\nData and emulated FDL vector size: identical.\n";

1860 for (

int iFdl = 0; iFdl < gtFdlVectorDataSize; ++iFdl) {

1861 const L1GtFdlWord& fdlBlockData = gtFdlVectorData[iFdl];

1862 const L1GtFdlWord& fdlBlockEmul = gtFdlVectorEmul[iFdl];

1867 m_myCoutStream <<

"\nData and emulated FDL vector size: different.\n";

1868 m_myCoutStream <<

" Data: size = " << gtFdlVectorDataSize << std::endl;

1869 m_myCoutStream <<

" Emul: size = " << gtFdlVectorEmulSize << std::endl;

1878 const std::vector<L1GtPsbWord>& gtPsbVectorData = gtReadoutRecordData->

gtPsbVector();

1879 const std::vector<L1GtPsbWord>& gtPsbVectorEmul = gtReadoutRecordEmul->

gtPsbVector();

1881 int gtPsbVectorDataSize = gtPsbVectorData.size();

1882 int gtPsbVectorEmulSize = gtPsbVectorEmul.size();

1884 if (gtPsbVectorDataSize == gtPsbVectorEmulSize) {

1885 m_myCoutStream <<

"\nData and emulated PSB vector size: identical.\n";

1888 m_myCoutStream <<

"\nData and emulated PSB vector size: different.\n";

1889 m_myCoutStream <<

" Data: size = " << gtPsbVectorDataSize << std::endl;

1890 m_myCoutStream <<

" Emul: size = " << gtPsbVectorEmulSize << std::endl;

1896 for (

int iPsb = 0; iPsb < gtPsbVectorDataSize; ++iPsb) {

1897 const L1GtPsbWord& psbBlockData = gtPsbVectorData[iPsb];

1898 const uint16_t boardIdData = psbBlockData.

boardId();

1899 const int bxInEventData = psbBlockData.

bxInEvent();

1904 bool foundPSB =

false;

1906 for (

int iPsbF = 0; iPsbF < gtPsbVectorEmulSize; ++iPsbF) {

1907 const L1GtPsbWord& psbBlockEmul = gtPsbVectorEmul[iPsbF];

1908 const uint16_t boardIdEmul = psbBlockEmul.

boardId();

1909 const int bxInEventEmul = psbBlockEmul.

bxInEvent();

1911 if ((boardIdEmul == boardIdData) && (bxInEventData == bxInEventEmul)) {

1920 m_myCoutStream <<

"\nNo emulated PSB with boardId() = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0')

1921 << boardIdData << std::setfill(

' ') <<

std::dec <<

" and BxInEvent = " << bxInEventData

References L1GtPsbWord::boardId(), L1GtPsbWord::bxInEvent(), compareFDL(), compareGTFE(), comparePSB(), TauDecayModes::dec, dqm::impl::MonitorElement::Fill(), L1GlobalTriggerReadoutRecord::gtFdlVector(), L1GlobalTriggerReadoutRecord::gtfeWord(), L1GlobalTriggerReadoutRecord::gtPsbVector(), iEvent, edm::HandleBase::isValid(), LogDebug, m_agree, m_dataOnly, m_dataOnlyMask, m_emulOnly, m_emulOnlyMask, m_gtErrorFlag, m_l1GtDataDaqInputToken_, m_l1GtEmulDaqInputToken_, m_myCoutStream, m_nrDataEventError, and m_nrEmulEventError.

Referenced by analyze().

◆ compareEvmRecord()

L1 GT EVM record comparison.

Definition at line 1947 of file L1GtHwValidation.cc.

1955 bool validData =

false;

1957 if (!gtReadoutRecordData.

isValid()) {

1967 bool validEmul =

false;

1969 if (!gtReadoutRecordEmul.

isValid()) {

1975 if ((!validData) || (!validEmul)) {

1976 edm::LogWarning(

"L1GtHwValidation") <<

"\n No valid product found: EVM L1GlobalTriggerEvmReadoutRecord"

1977 <<

"\n Data validity [1 = true; 0 = false]: " << validData

1978 <<

"\n Emulator validity: [1 = true; 0 = false]: " << validEmul

1979 <<

"\n EVM histograms will not be filled.\n"

1992 const std::vector<L1GtFdlWord>& gtFdlVectorData = gtReadoutRecordData->

gtFdlVector();

1993 const std::vector<L1GtFdlWord>& gtFdlVectorEmul = gtReadoutRecordEmul->

gtFdlVector();

1995 int gtFdlVectorDataSize = gtFdlVectorData.size();

1996 int gtFdlVectorEmulSize = gtFdlVectorEmul.size();

1998 if (gtFdlVectorDataSize == gtFdlVectorEmulSize) {

1999 m_myCoutStream <<

"\nData and emulated FDL vector size: identical.\n";

2002 for (

int iFdl = 0; iFdl < gtFdlVectorDataSize; ++iFdl) {

2003 const L1GtFdlWord& fdlBlockData = gtFdlVectorData[iFdl];

2004 const L1GtFdlWord& fdlBlockEmul = gtFdlVectorEmul[iFdl];

2009 m_myCoutStream <<

"\nData and emulated FDL vector size: different.\n";

2010 m_myCoutStream <<

" Data: size = " << gtFdlVectorDataSize << std::endl;

2011 m_myCoutStream <<

" Emul: size = " << gtFdlVectorEmulSize << std::endl;

References compareFDL(), compareGTFE(), L1GlobalTriggerEvmReadoutRecord::gtFdlVector(), L1GlobalTriggerEvmReadoutRecord::gtfeWord(), iEvent, edm::HandleBase::isValid(), LogDebug, m_l1GtDataEvmInputToken_, m_l1GtEmulEvmInputToken_, m_myCoutStream, m_nrDataEventError, and m_nrEmulEventError.

Referenced by analyze().

◆ compareFDL()

compare the FDL board

Definition at line 974 of file L1GtHwValidation.cc.

980 int PhysicsPartition = 0;

985 if (fdlBlockData == fdlBlockEmul) {

986 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL blocks: identical.\n";

990 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL blocks: different.\n";

1006 const int bxInEventData = fdlBlockData.

bxInEvent();

1007 const int bxInEventEmul = fdlBlockEmul.

bxInEvent();

1009 bool matchBxInEvent =

false;

1011 if (bxInEventData == bxInEventEmul) {

1012 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL bxInEvent identical.";

1015 matchBxInEvent =

true;

1018 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL bxInEvent different.";

1029 <<

"\n Data and emulated FDL bxInEvent different \n";

1038 bool validBxInEvent =

false;

1040 LogDebug(

"L1GtHwValidation") <<

"\n Convert bxInEvent = " << bxInEventData <<

" to histIndex = " << histIndex

1043 validBxInEvent =

true;

1049 const uint16_t boardIdData = fdlBlockData.

boardId();

1050 const uint16_t boardIdEmul = fdlBlockEmul.

boardId();

1052 if (boardIdData == boardIdEmul) {

1053 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL boardId identical.";

1054 m_myCoutStream <<

"\n boardId() = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0') << boardIdData

1059 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL boardId different.";

1060 m_myCoutStream <<

"\n Data: boardId() = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0') << boardIdData

1062 m_myCoutStream <<

"\n Emul: boardId() = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0') << boardIdEmul

1066 if (matchBxInEvent && validBxInEvent) {

1078 const uint16_t bxNrData = fdlBlockData.

bxNr();

1079 const uint16_t bxNrEmul = fdlBlockEmul.

bxNr();

1081 if (bxNrData == bxNrEmul) {

1082 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL bxNr identical.";

1087 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL bxNr different.";

1092 if (matchBxInEvent && validBxInEvent) {

1104 const uint32_t eventNrData = fdlBlockData.

eventNr();

1105 const uint32_t eventNrEmul = fdlBlockEmul.

eventNr();

1107 if (eventNrData == eventNrEmul) {

1108 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL eventNr identical.";

1113 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL eventNr different.";

1118 if (matchBxInEvent && validBxInEvent) {

1133 int nTechBits = gtTechnicalTriggerWordData.size();

1138 unsigned int bitValue = 0;

1140 if (matchBxInEvent && validBxInEvent) {

1141 for (

int iBit = 0; iBit < nTechBits; ++iBit) {

1144 if (gtTechnicalTriggerWordData[iBit]) {

1147 bitValue = (triggerMask) ? 0 : 1;

1148 gtTechnicalTriggerWordDataMask[iBit] = bitValue;

1154 if (gtTechnicalTriggerWordEmul.at(iBit)) {

1157 bitValue = (triggerMask) ? 0 : 1;

1158 gtTechnicalTriggerWordEmulMask[iBit] = bitValue;

1165 for (

int iBit = 0; iBit < nTechBits; ++iBit) {

1166 if (gtTechnicalTriggerWordData[iBit]) {

1170 if (gtTechnicalTriggerWordEmul.at(iBit)) {

1176 if (gtTechnicalTriggerWordData == gtTechnicalTriggerWordEmul) {

1177 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL gtTechnicalTriggerWord identical.\n";

1182 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL gtTechnicalTriggerWord different.";

1189 if (matchBxInEvent && validBxInEvent) {

1195 if (matchBxInEvent && validBxInEvent) {

1196 for (

int iBit = 0; iBit < nTechBits; ++iBit) {

1197 if (gtTechnicalTriggerWordData[iBit] != gtTechnicalTriggerWordEmul.at(iBit)) {

1202 for (

int iBit = 0; iBit < nTechBits; ++iBit) {

1203 if (gtTechnicalTriggerWordData[iBit] != gtTechnicalTriggerWordEmul.at(iBit)) {

1214 if (gtTechnicalTriggerWordDataMask == gtTechnicalTriggerWordEmulMask) {

1215 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL gtTechnicalTriggerWord after mask identical.\n";

1219 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL gtTechnicalTriggerWord after mask different.";

1224 if (matchBxInEvent && validBxInEvent) {

1230 if (matchBxInEvent && validBxInEvent) {

1231 for (

int iBit = 0; iBit < nTechBits; ++iBit) {

1232 if (gtTechnicalTriggerWordData[iBit] != gtTechnicalTriggerWordEmul.at(iBit)) {

1247 int nAlgoBits = gtDecisionWordData.size();

1257 size_t pfSetsSize = (*m_prescaleFactorsAlgoTrig).size();

1260 LogDebug(

"L1GtHwValidation") <<

"\nError: index of prescale factor set retrieved from the data \n"

1261 <<

"less than zero."

1262 <<

"\n Value of index retrieved from data = " << iPfSet << std::endl;

1268 }

else if (iPfSet >= (static_cast<int>(pfSetsSize))) {

1269 LogDebug(

"L1GtHwValidation") <<

"\nError: index of prescale factor set retrieved from the data \n"

1270 <<

"greater than the size of the vector of prescale factor sets."

1271 <<

"\n Value of index retrieved from data = " << iPfSet

1272 <<

"\n Vector size = " << pfSetsSize << std::endl;

1279 const std::vector<int>& prescaleFactorsAlgoTrig = (*m_prescaleFactorsAlgoTrig).at(iPfSet);

1281 if (matchBxInEvent && validBxInEvent) {

1282 for (

int iBit = 0; iBit < nAlgoBits; ++iBit) {

1288 <<

" trigger mask = " << triggerMask << std::endl;

1290 if (gtDecisionWordData[iBit]) {

1299 bitValue = (triggerMask) ? 0 : 1;

1300 gtDecisionWordDataMask[iBit] = bitValue;

1306 if (gtDecisionWordEmul.at(iBit)) {

1309 bitValue = (triggerMask) ? 0 : 1;

1310 gtDecisionWordEmulMask[iBit] = bitValue;

1317 for (

int iBit = 0; iBit < nAlgoBits; ++iBit) {

1318 if (gtDecisionWordData[iBit]) {

1323 for (

int iBit = 0; iBit < nAlgoBits; ++iBit) {

1324 if (gtDecisionWordEmul.at(iBit)) {

1333 <<

"\n matchBxInEvent && validBxInEvent false \n";

1337 if (gtDecisionWordData == gtDecisionWordEmul) {

1338 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL gtDecisionWord identical.";

1343 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL gtDecisionWord different.";

1350 if (matchBxInEvent && validBxInEvent) {

1356 if (matchBxInEvent && validBxInEvent) {

1357 for (

int iBit = 0; iBit < nAlgoBits; ++iBit) {

1360 if (gtDecisionWordData[iBit] != gtDecisionWordEmul.at(iBit)) {

1364 if (

excludedAlgo(iBit) && (bxInEventData == 0) && (iRec == 0)) {

1380 if (gtDecisionWordData[iBit]) {

1388 if ((!

excludedAlgo(iBit)) && (bxInEventData == 0) && (iRec == 0)) {

1393 <<

"result before mask for algorithm with bit number " << iBit

1394 <<

"\n Data: true, emulator: false \n";

1409 if ((!

excludedAlgo(iBit)) && (bxInEventData == 0) && (iRec == 0)) {

1414 <<

"result before mask for algorithm with bit number " << iBit

1415 <<

"\n Data: false, emulator: true \n";

1425 for (

int iBit = 0; iBit < nAlgoBits; ++iBit) {

1426 if (gtDecisionWordData[iBit] != gtDecisionWordEmul.at(iBit)) {

1435 <<

"\n matchBxInEvent && validBxInEvent false \n";

1440 if (gtDecisionWordDataMask == gtDecisionWordEmulMask) {

1441 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL gtDecisionWord after mask identical.";

1445 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL gtDecisionWord after mask different.";

1450 if (matchBxInEvent && validBxInEvent) {

1456 if (matchBxInEvent && validBxInEvent) {

1457 for (

int iBit = 0; iBit < nAlgoBits; ++iBit) {

1458 if (gtDecisionWordDataMask[iBit] != gtDecisionWordEmulMask.at(iBit)) {

1463 if (gtDecisionWordDataMask[iBit]) {

1471 if ((!

excludedAlgo(iBit)) && (bxInEventData == 0) && (iRec == 0)) {

1476 <<

"result after mask for algorithm with bit number " << iBit

1477 <<

" different in data versus emulator "

1478 <<

"\n Data: true, emulator: false \n";

1493 if ((!

excludedAlgo(iBit)) && (bxInEventData == 0) && (iRec == 0)) {

1498 <<

"result after mask for algorithm with bit number " << iBit

1499 <<

" different in data versus emulator "

1500 <<

"\n Data: false, emulator: true \n";

1516 if (gtDecisionWordExtendedData == gtDecisionWordExtendedEmul) {

1517 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL gtDecisionWordExtended identical.\n";

1522 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL gtDecisionWordExtended different.\n";

1529 if (matchBxInEvent && validBxInEvent) {

1537 const uint16_t noAlgoData = fdlBlockData.

noAlgo();

1538 const uint16_t noAlgoEmul = fdlBlockEmul.

noAlgo();

1540 if (noAlgoData == noAlgoEmul) {

1541 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL noAlgo identical.";

1546 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL noAlgo different.";

1551 if (matchBxInEvent && validBxInEvent) {

1559 const uint16_t finalORData = fdlBlockData.

finalOR();

1560 const uint16_t finalOREmul = fdlBlockEmul.

finalOR();

1562 if (finalORData == finalOREmul) {

1563 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL finalOR identical.";

1564 m_myCoutStream <<

"\n finalOR() = " << std::hex <<

"0x" << std::setw(2) << std::setfill(

'0') << finalORData

1569 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL finalOR different.";

1570 m_myCoutStream <<

"\n Data: finalOR() = " << std::hex <<

"0x" << std::setw(2) << std::setfill(

'0') << finalORData

1572 m_myCoutStream <<

"\n Emul: finalOR() = " << std::hex <<

"0x" << std::setw(2) << std::setfill(

'0') << finalOREmul

1576 if (matchBxInEvent && validBxInEvent) {

1584 const int finalORPhysData = finalORData & (1 << PhysicsPartition);

1585 const int finalORPhysEmul = finalOREmul & (1 << PhysicsPartition);

1587 if (finalORPhysData == finalORPhysEmul) {

1588 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL finalOR for the physics partition identical.";

1593 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL finalOR for the physics partition different.";

1598 if (matchBxInEvent && validBxInEvent) {

1606 const uint16_t localBxNrData = fdlBlockData.

localBxNr();

1607 const uint16_t localBxNrEmul = fdlBlockEmul.

localBxNr();

1609 if (localBxNrData == localBxNrEmul) {

1610 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL localBxNr identical.";

1615 m_myCoutStream <<

"\n" << recString <<

" Data and emulated FDL localBxNr different.";

1620 if (matchBxInEvent && validBxInEvent) {

References L1GtFdlWord::boardId(), L1GtFdlWord::bxInEvent(), L1GtFdlWord::bxNr(), TauDecayModes::dec, L1GtFdlWord::eventNr(), excludedAlgo(), dqm::impl::MonitorElement::Fill(), L1GtFdlWord::finalOR(), L1GtFdlWord::gtDecisionWord(), L1GtFdlWord::gtDecisionWordExtended(), L1GtFdlWord::gtPrescaleFactorIndexAlgo(), L1GtFdlWord::gtTechnicalTriggerWord(), L1GtFdlWord::localBxNr(), LogDebug, LogTrace, m_agree, m_dataOnly, m_dataOnlyMask, m_emulOnly, m_emulOnlyMask, m_excludedAlgorithmsAgreement, m_fdlDataAlgoDecision, m_fdlDataAlgoDecision_Err, m_fdlDataAlgoDecision_NoMatch, m_fdlDataAlgoDecisionMask, m_fdlDataAlgoDecisionMask_NoMatch, m_fdlDataAlgoDecisionPrescaled, m_fdlDataAlgoDecisionPrescaled_NoMatch, m_fdlDataAlgoDecisionPrescaledMask_NoMatch, m_fdlDataAlgoDecisionUnprescaled, m_fdlDataAlgoDecisionUnprescaled_NoMatch, m_fdlDataAlgoDecisionUnprescaledMask_NoMatch, m_fdlDataEmul, m_fdlDataEmul_Err, m_fdlDataEmulAlgoDecision, m_fdlDataEmulAlgoDecision_Err, m_fdlDataEmulAlgoDecisionMask, m_fdlDataEmulAlgoDecisionPrescaled, m_fdlDataEmulAlgoDecisionUnprescaled, m_fdlDataEmulAlgoDecisionUnprescaledAllowed, m_fdlDataEmulTechDecision, m_fdlDataEmulTechDecision_Err, m_fdlDataEmulTechDecisionMask, m_fdlDataTechDecision, m_fdlDataTechDecision_Err, m_fdlDataTechDecisionMask, m_fdlEmulAlgoDecision, m_fdlEmulAlgoDecision_Err, m_fdlEmulAlgoDecision_NoMatch, m_fdlEmulAlgoDecisionMask, m_fdlEmulAlgoDecisionMask_NoMatch, m_fdlEmulAlgoDecisionPrescaled_NoMatch, m_fdlEmulAlgoDecisionPrescaledMask_NoMatch, m_fdlEmulAlgoDecisionUnprescaled_NoMatch, m_fdlEmulAlgoDecisionUnprescaledMask_NoMatch, m_fdlEmulTechDecision, m_fdlEmulTechDecision_Err, m_fdlEmulTechDecisionMask, m_myCoutStream, m_triggerMaskAlgoTrig, m_triggerMaskTechTrig, L1GtFdlWord::noAlgo(), Skims_PDWG_cff::prescaleFactor, L1GtFdlWord::print(), L1GtFdlWord::printGtDecisionWord(), L1GtFdlWord::printGtDecisionWordExtended(), L1GtFdlWord::printGtTechnicalTriggerWord(), AlCaHLTBitMon_QueryRunRegistry::string, and TotalBxInEvent.

Referenced by compareDaqRecord(), and compareEvmRecord().

◆ compareGt_Gct()

compare the GCT collections obtained from L1 GT PSB with the input GCT collections

Definition at line 2029 of file L1GtHwValidation.cc.

Referenced by analyze().

◆ compareGTFE()

compare the GTFE board

get record length for alternative 1

get record length for alternative 0

get bunch cross number as counted in the GTFE board

get setup version

get boards contributing to EVM respectively DAQ record

alternative for number of BX per board correlated with active boards bit value is 0: take alternative 0 bit value is 1: take alternative 1

get total number of L1A sent since start of run

Definition at line 800 of file L1GtHwValidation.cc.

806 if (gtfeBlockData == gtfeBlockEmul) {

807 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE blocks: identical.\n";

810 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE blocks: different.\n";

825 const uint16_t boardIdData = gtfeBlockData.

boardId();

826 const uint16_t boardIdEmul = gtfeBlockEmul.

boardId();

828 if (boardIdData == boardIdEmul) {

829 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE boardId identical.";

830 m_myCoutStream <<

"\n boardId() = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0') << boardIdData

835 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE boardId different.";

836 m_myCoutStream <<

"\n Data: boardId() = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0') << boardIdData

838 m_myCoutStream <<

"\n Emul: boardId() = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0') << boardIdEmul

845 const uint16_t recordLength1Data = gtfeBlockData.

recordLength1();

846 const uint16_t recordLength1Emul = gtfeBlockEmul.

recordLength1();

848 if (recordLength1Data == recordLength1Emul) {

849 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE recordLength for alternative 1 identical.";

854 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE recordLength for alternative 1 different.";

855 m_myCoutStream <<

"\n Data: recordLength1() = " << recordLength1Data;

856 m_myCoutStream <<

"\n Emul: recordLength1() = " << recordLength1Emul;

862 const uint16_t recordLengthData = gtfeBlockData.

recordLength();

863 const uint16_t recordLengthEmul = gtfeBlockEmul.

recordLength();

865 if (recordLengthData == recordLengthEmul) {

866 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE recordLength for alternative 0 identical.";

871 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE recordLength for alternative 1 different.";

872 m_myCoutStream <<

"\n Data: recordLength() = " << recordLengthData;

873 m_myCoutStream <<

"\n Emul: recordLength() = " << recordLengthEmul;

879 const uint16_t bxNrData = gtfeBlockData.

bxNr();

880 const uint16_t bxNrEmul = gtfeBlockEmul.

bxNr();

882 if (bxNrData == bxNrEmul) {

883 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE bxNr identical.";

888 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE bxNr different.";

896 const uint32_t setupVersionData = gtfeBlockData.

setupVersion();

897 const uint32_t setupVersionEmul = gtfeBlockEmul.

setupVersion();

899 if (setupVersionData == setupVersionEmul) {

900 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE setupVersion identical.";

905 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE setupVersion different.";

906 m_myCoutStream <<

"\n Data: setupVersion() = " << setupVersionData;

907 m_myCoutStream <<

"\n Emul: setupVersion() = " << setupVersionEmul;

913 const uint16_t activeBoardsData = gtfeBlockData.

activeBoards();

914 const uint16_t activeBoardsEmul = gtfeBlockEmul.

activeBoards();

916 if (activeBoardsData == activeBoardsEmul) {

917 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE activeBoards identical.";

918 m_myCoutStream <<

"\n activeBoards() = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0')

919 << activeBoardsData << std::setfill(

' ') <<

std::dec;

923 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE activeBoards different.";

924 m_myCoutStream <<

"\n Data: activeBoards() = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0')

925 << activeBoardsData << std::setfill(

' ') <<

std::dec;

926 m_myCoutStream <<

"\n Emul: activeBoards() = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0')

927 << activeBoardsEmul << std::setfill(

' ') <<

std::dec;

935 const uint16_t altNrBxBoardData = gtfeBlockData.

altNrBxBoard();

936 const uint16_t altNrBxBoardEmul = gtfeBlockEmul.

altNrBxBoard();

938 if (altNrBxBoardData == altNrBxBoardEmul) {

939 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE altNrBxBoard identical.";

944 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE altNrBxBoard different.";

945 m_myCoutStream <<

"\n Data: altNrBxBoard() = " << altNrBxBoardData;

946 m_myCoutStream <<

"\n Emul: altNrBxBoard() = " << altNrBxBoardEmul;

952 const uint32_t totalTriggerNrData = gtfeBlockData.

totalTriggerNr();

953 const uint32_t totalTriggerNrEmul = gtfeBlockEmul.

totalTriggerNr();

955 if (totalTriggerNrData == totalTriggerNrEmul) {

956 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE totalTriggerNr identical.";

961 m_myCoutStream <<

"\n" << recString <<

" Data and emulated GTFE totalTriggerNr different.";

962 m_myCoutStream <<

"\n Data: totalTriggerNr() = " << totalTriggerNrData;

963 m_myCoutStream <<

"\n Emul: totalTriggerNr() = " << totalTriggerNrEmul;

References L1GtfeWord::activeBoards(), L1GtfeWord::altNrBxBoard(), L1GtfeWord::boardId(), L1GtfeWord::bxNr(), TauDecayModes::dec, dqm::impl::MonitorElement::Fill(), LogDebug, m_gtfeDataEmul, m_myCoutStream, L1GtfeWord::print(), L1GtfeWord::recordLength(), L1GtfeWord::recordLength1(), L1GtfeWord::setupVersion(), AlCaHLTBitMon_QueryRunRegistry::string, and L1GtfeWord::totalTriggerNr().

Referenced by compareDaqRecord(), and compareEvmRecord().

◆ comparePSB()

compare the PSB board

get/set A_DATA_CH_IA

get/set B_DATA_CH_IB

Definition at line 1633 of file L1GtHwValidation.cc.

1637 if (psbBlockData == psbBlockEmul) {

1638 m_myCoutStream <<

"\nData and emulated PSB blocks: identical.\n";

1642 m_myCoutStream <<

"\nData and emulated PSB blocks: different.\n";

1657 const uint16_t boardIdData = psbBlockData.

boardId();

1658 const uint16_t boardIdEmul = psbBlockEmul.

boardId();

1660 if (boardIdData == boardIdEmul) {

1662 m_myCoutStream <<

"\n boardId() = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0') << boardIdData

1668 m_myCoutStream <<

"\n Data: boardId() = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0') << boardIdData

1670 m_myCoutStream <<

"\n Emul: boardId() = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0') << boardIdEmul

1676 const int bxInEventData = psbBlockData.

bxInEvent();

1677 const int bxInEventEmul = psbBlockEmul.

bxInEvent();

1679 if (bxInEventData == bxInEventEmul) {

1680 m_myCoutStream <<

"\nData and emulated PSB bxInEvent identical.";

1685 m_myCoutStream <<

"\nData and emulated PSB bxInEvent different.";

1692 const uint16_t bxNrData = psbBlockData.

bxNr();

1693 const uint16_t bxNrEmul = psbBlockEmul.

bxNr();

1695 if (bxNrData == bxNrEmul) {

1708 const uint32_t eventNrData = psbBlockData.

eventNr();

1709 const uint32_t eventNrEmul = psbBlockEmul.

eventNr();

1711 if (eventNrData == eventNrEmul) {

1727 for (

int iA = 0; iA < psbBlockData.

NumberAData; ++iA) {

1728 valData = psbBlockData.

aData(iA);

1729 valEmul = psbBlockEmul.

aData(iA);

1731 if (valData == valEmul) {

1732 m_myCoutStream <<

"\nData and emulated PSB aData(" << iA <<

") identical.";

1733 m_myCoutStream <<

"\n aData(iA) = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0') << valData

1738 m_myCoutStream <<

"\nData and emulated PSB aData(" << iA <<

") different.";

1739 m_myCoutStream <<

"\n Data: aData(iA) = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0') << valData

1741 m_myCoutStream <<

"\n Emul: aData(iA) = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0') << valEmul

1748 for (

int iB = 0; iB < psbBlockData.

NumberBData; ++iB) {

1749 valData = psbBlockData.

bData(iB);

1750 valEmul = psbBlockEmul.

bData(iB);

1752 if (valData == valEmul) {

1753 m_myCoutStream <<

"\nData and emulated PSB bData(" << iB <<

") identical.";

1754 m_myCoutStream <<

"\n bData(iA) = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0') << valData

1759 m_myCoutStream <<

"\nData and emulated PSB bData(" << iB <<

") different.";

1760 m_myCoutStream <<

"\n Data: bData(iA) = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0') << valData

1762 m_myCoutStream <<

"\n Emul: bData(iA) = " << std::hex <<

"0x" << std::setw(4) << std::setfill(

'0') << valEmul

1769 const uint16_t localBxNrData = psbBlockData.

localBxNr();

1770 const uint16_t localBxNrEmul = psbBlockEmul.

localBxNr();

1772 if (localBxNrData == localBxNrEmul) {

1773 m_myCoutStream <<

"\nData and emulated PSB localBxNr identical.";

1778 m_myCoutStream <<

"\nData and emulated PSB localBxNr different.";

References L1GtPsbWord::aData(), L1GtPsbWord::bData(), L1GtPsbWord::boardId(), L1GtPsbWord::bxInEvent(), L1GtPsbWord::bxNr(), TauDecayModes::dec, L1GtPsbWord::eventNr(), L1GtPsbWord::localBxNr(), LogDebug, m_myCoutStream, L1GtPsbWord::NumberAData, L1GtPsbWord::NumberBData, and L1GtPsbWord::print().

Referenced by compareDaqRecord().

◆ compareTCS()

◆ excludedAlgo()

| bool L1GtHwValidation::excludedAlgo |

( |

const int & |

iBit | ) |

const |

|

private |

◆ excludedAlgoList()

| void L1GtHwValidation::excludedAlgoList |

( |

| ) |

|

|

private |

exclude from comparison some bits with known disagreement - bit list

Definition at line 2096 of file L1GtHwValidation.cc.

2099 for (

CItAlgo itAlgo = algorithmMap.begin(); itAlgo != algorithmMap.end(); itAlgo++) {

2101 const int algBitNumber = (itAlgo->second).algoBitNumber();

2102 const int chipNr = (itAlgo->second).algoChipNumber();

2106 const std::vector<L1GtLogicParser::TokenRPN>& aRpnVector = (itAlgo->second).algoRpnVector();

2107 size_t aRpnVectorSize = aRpnVector.size();

2109 bool algWithExcludedCondition =

false;

2110 bool algWithConditionNotInMap =

false;

2113 for (

size_t opI = 0; opI < aRpnVectorSize; ++opI) {

2114 const std::string& cndName = (aRpnVector[opI]).operand;

2116 if (!cndName.empty()) {

2117 bool foundCond =

false;

2119 CItCond itCond = conditionMap.find(cndName);

2120 if (itCond != conditionMap.end()) {

2123 const std::vector<L1GtObject>&

objType = (itCond->second)->objectType();

2137 LogTrace(

"L1GtHwValidation") <<

"\n "

2138 <<

"Algorithm: " << algName <<

" Condition: " << cndName <<

"\n "

2143 <<

"Object excluded: "

2146 if (matchCondCategoryValue && matchCondTypeValue && matchCondL1GtObjectValue) {

2147 algWithExcludedCondition =

true;

2157 algWithConditionNotInMap =

true;

2159 LogTrace(

"L1GtHwValidation") <<

"\n Error: condition " << cndName <<

" not found in condition map!"

2160 <<

"\n Add algorithm " << algName <<

" (bit number " << algBitNumber <<

") "

2161 <<

"\n to list of algorithms excluded from comparison"

2162 <<

"\n data versus emulator." << std::endl;

2167 if (algWithConditionNotInMap) {

2172 LogTrace(

"L1GtHwValidation") <<

"\n Error: one or more conditions from algorithm " << algName <<

" (bit number "

2173 << algBitNumber <<

") "

2174 <<

" not found in condition map!"

2175 <<

"\n Add it to list of algorithms excluded from comparison"

2176 <<

"\n data versus emulator." << std::endl;

2179 if (algWithExcludedCondition) {

2182 LogTrace(

"L1GtHwValidation") <<

"\n Algorithm " << algName <<

" (bit number " << algBitNumber

2183 <<

") contains an excluded condition."

2184 <<

"\n Add it to list of algorithms excluded from comparison"

2185 <<

"\n data versus emulator." << std::endl;

2192 if ((*itExcl) == algName) {

2195 LogTrace(

"L1GtHwValidation") <<

"\n Algorithm " << algName <<

" (bit number " << algBitNumber

2196 <<

")\n added to list of algorithms excluded from comparison"

2197 <<

" \n data versus emulator by ExcludeAlgoTrigByName." << std::endl;

2205 if ((*itExcl) == algBitNumber) {

2208 LogTrace(

"L1GtHwValidation") <<

"\n Algorithm " << algName <<

" (bit number " << algBitNumber

2209 <<

")\n added to list of algorithms excluded from comparison"

2210 <<

" \n data versus emulator by ExcludeAlgoTrigByBit." << std::endl;

References L1GtTriggerMenu::gtAlgorithmMap(), L1GtTriggerMenu::gtConditionMap(), l1GtConditionCategoryEnumToString(), l1GtConditionTypeEnumToString(), l1GtObjectEnumToString(), LogTrace, m_excludeAlgoTrigByBit, m_excludeAlgoTrigByName, m_excludedAlgoList, m_excludedCondCategory, m_excludedCondType, m_excludedL1GtObject, m_l1GtMenu, matchCondCategory(), matchCondL1GtObject(), matchCondType(), electrons_cff::objType, and AlCaHLTBitMon_QueryRunRegistry::string.

Referenced by bookHistograms().

◆ matchCondCategory()

book all histograms for the module

return true if an algorithm has a condition of that category for CondNull, it returns always true

Definition at line 2048 of file L1GtHwValidation.cc.

2050 bool matchValue =

false;

2052 if (excludedCategory ==

CondNull) {

2055 if (conditionCategory == excludedCategory) {

References CondNull.

Referenced by excludedAlgoList().

◆ matchCondL1GtObject()

| bool L1GtHwValidation::matchCondL1GtObject |

( |

const std::vector< L1GtObject > & |

condObjects, |

|

|

const L1GtObject & |

excludedObject |

|

) |

| |

|

private |

return true if an algorithm has a condition containing that object for ObjNull, it returns always true

Definition at line 2077 of file L1GtHwValidation.cc.

2079 bool matchValue =

false;

2081 if (excludedObject ==

ObjNull) {

2085 for (std::vector<L1GtObject>::const_iterator itCondObj = condObjects.begin(); itCondObj != condObjects.end();

2087 if ((*itCondObj) == excludedObject) {

References ObjNull.

Referenced by excludedAlgoList().

◆ matchCondType()

◆ l1gtPrescaleAlgoToken_

◆ l1gtPrescaleTechToken_

◆ l1gtTrigmaskAlgoToken_

◆ l1gtTrigmaskTechToken_

◆ l1gtTrigmenuToken_

◆ m_agree

| bool L1GtHwValidation::m_agree |

|

private |

◆ m_dataOnly

| bool L1GtHwValidation::m_dataOnly |

|

private |

◆ m_dataOnlyMask

| bool L1GtHwValidation::m_dataOnlyMask |

|

private |

◆ m_dirName

| std::string L1GtHwValidation::m_dirName |

|

private |

◆ m_emulOnly

| bool L1GtHwValidation::m_emulOnly |

|

private |

◆ m_emulOnlyMask

| bool L1GtHwValidation::m_emulOnlyMask |

|

private |

◆ m_excludeAlgoTrigByBit

| std::vector<int> L1GtHwValidation::m_excludeAlgoTrigByBit |

|

private |

◆ m_excludeAlgoTrigByName

| std::vector<std::string> L1GtHwValidation::m_excludeAlgoTrigByName |

|

private |

◆ m_excludeCondCategTypeObject

◆ m_excludedAlgoList

| std::vector<int> L1GtHwValidation::m_excludedAlgoList |

|

private |

◆ m_excludedAlgorithmsAgreement

◆ m_excludedCondCategory

◆ m_excludedCondType

◆ m_excludedL1GtObject

| std::vector<L1GtObject> L1GtHwValidation::m_excludedL1GtObject |

|

private |

◆ m_fdlDataAlgoDecision

◆ m_fdlDataAlgoDecision_Err

◆ m_fdlDataAlgoDecision_NoMatch

◆ m_fdlDataAlgoDecisionMask

◆ m_fdlDataAlgoDecisionMask_NoMatch

◆ m_fdlDataAlgoDecisionPrescaled

◆ m_fdlDataAlgoDecisionPrescaled_NoMatch

◆ m_fdlDataAlgoDecisionPrescaledMask_NoMatch

◆ m_fdlDataAlgoDecisionUnprescaled

◆ m_fdlDataAlgoDecisionUnprescaled_NoMatch

◆ m_fdlDataAlgoDecisionUnprescaledMask_NoMatch

◆ m_fdlDataEmul

◆ m_fdlDataEmul_Err

◆ m_fdlDataEmulAlgoDecision

◆ m_fdlDataEmulAlgoDecision_Err

◆ m_fdlDataEmulAlgoDecisionMask

◆ m_fdlDataEmulAlgoDecisionPrescaled

◆ m_fdlDataEmulAlgoDecisionUnprescaled

◆ m_fdlDataEmulAlgoDecisionUnprescaledAllowed

◆ m_fdlDataEmulTechDecision

◆ m_fdlDataEmulTechDecision_Err

◆ m_fdlDataEmulTechDecisionMask

◆ m_fdlDataTechDecision

◆ m_fdlDataTechDecision_Err

◆ m_fdlDataTechDecisionMask

◆ m_fdlEmulAlgoDecision

◆ m_fdlEmulAlgoDecision_Err

◆ m_fdlEmulAlgoDecision_NoMatch

◆ m_fdlEmulAlgoDecisionMask

◆ m_fdlEmulAlgoDecisionMask_NoMatch

◆ m_fdlEmulAlgoDecisionPrescaled

◆ m_fdlEmulAlgoDecisionPrescaled_NoMatch

◆ m_fdlEmulAlgoDecisionPrescaledMask_NoMatch

◆ m_fdlEmulAlgoDecisionUnprescaled

◆ m_fdlEmulAlgoDecisionUnprescaled_NoMatch

◆ m_fdlEmulAlgoDecisionUnprescaledMask_NoMatch

◆ m_fdlEmulTechDecision

◆ m_fdlEmulTechDecision_Err

◆ m_fdlEmulTechDecisionMask

◆ m_gtErrorFlag

◆ m_gtfeDataEmul

◆ m_l1GctDataInputTag

◆ m_l1GtDataDaqInputTag

◆ m_l1GtDataDaqInputToken_

◆ m_l1GtDataEvmInputTag

◆ m_l1GtDataEvmInputToken_

◆ m_l1GtEmulDaqInputTag

◆ m_l1GtEmulDaqInputToken_

◆ m_l1GtEmulEvmInputTag

◆ m_l1GtEmulEvmInputToken_

◆ m_l1GtMenu

◆ m_l1GtMenuCacheID

| unsigned long long L1GtHwValidation::m_l1GtMenuCacheID |

|

private |

◆ m_l1GtPfAlgo

◆ m_l1GtPfAlgoCacheID

| unsigned long long L1GtHwValidation::m_l1GtPfAlgoCacheID |

|

private |

◆ m_l1GtPfTech

◆ m_l1GtPfTechCacheID

| unsigned long long L1GtHwValidation::m_l1GtPfTechCacheID |

|

private |

◆ m_l1GtTmAlgo

◆ m_l1GtTmAlgoCacheID

| unsigned long long L1GtHwValidation::m_l1GtTmAlgoCacheID |

|

private |

◆ m_l1GtTmTech

◆ m_l1GtTmTechCacheID

| unsigned long long L1GtHwValidation::m_l1GtTmTechCacheID |

|

private |

◆ m_myCoutStream

| std::ostringstream L1GtHwValidation::m_myCoutStream |

|

private |

◆ m_nrDataEventError

| int L1GtHwValidation::m_nrDataEventError |

|

private |

◆ m_nrEmulEventError

| int L1GtHwValidation::m_nrEmulEventError |

|

private |

◆ m_nrEvJob

| int L1GtHwValidation::m_nrEvJob |

|

private |

◆ m_nrEvRun

| int L1GtHwValidation::m_nrEvRun |

|

private |

◆ m_prescaleFactorsAlgoTrig

| const std::vector<std::vector<int> >* L1GtHwValidation::m_prescaleFactorsAlgoTrig |

|

private |

◆ m_prescaleFactorsTechTrig

| const std::vector<std::vector<int> >* L1GtHwValidation::m_prescaleFactorsTechTrig |

|

private |

◆ m_triggerMaskAlgoTrig

| std::vector<unsigned int> L1GtHwValidation::m_triggerMaskAlgoTrig |

|

private |

◆ m_triggerMaskTechTrig

| std::vector<unsigned int> L1GtHwValidation::m_triggerMaskTechTrig |

|

private |

◆ NumberOfGtRecords

| const int L1GtHwValidation::NumberOfGtRecords = 2 |

|

staticprivate |

◆ TotalBxInEvent

| const int L1GtHwValidation::TotalBxInEvent = 5 |

|

staticprivate |

MonitorElement * m_fdlEmulTechDecisionMask[TotalBxInEvent][NumberOfGtRecords]

bool m_agree

internal members

unsigned long long m_l1GtTmAlgoCacheID

MonitorElement * m_gtfeDataEmul[NumberOfGtRecords]

histograms

edm::InputTag m_l1GtDataDaqInputTag

input tag for the L1 GT hardware DAQ record

edm::ESGetToken< L1GtPrescaleFactors, L1GtPrescaleFactorsTechTrigRcd > l1gtPrescaleTechToken_

const cms_uint16_t activeBoards() const

get/set boards contributing to EVM respectively DAQ record

MonitorElement * m_fdlDataAlgoDecisionMask_NoMatch[TotalBxInEvent][NumberOfGtRecords]

const int bxInEvent() const

get/set bunch cross in the GT event record

const L1GtTriggerMenu * m_l1GtMenu

trigger menu

MonitorElement * m_fdlDataEmulAlgoDecisionMask[TotalBxInEvent][NumberOfGtRecords]

const cms_uint16_t aData(int iA) const

get/set A_DATA_CH_IA

MonitorElement * m_fdlDataEmul[TotalBxInEvent][NumberOfGtRecords]

FDL (0 for DAQ, 1 for EVM record)

virtual void compareGt_Gct(const edm::Event &, const edm::EventSetup &)

MonitorElement * m_excludedAlgorithmsAgreement

const cms_uint16_t gtPrescaleFactorIndexAlgo() const

MonitorElement * m_fdlEmulAlgoDecisionUnprescaledMask_NoMatch[TotalBxInEvent][NumberOfGtRecords]

edm::EDGetTokenT< L1GlobalTriggerReadoutRecord > m_l1GtEmulDaqInputToken_

std::string l1GtObjectEnumToString(const L1GtObject &)

int m_nrDataEventError

counters

MonitorElement * m_fdlEmulAlgoDecision_Err[NumberOfGtRecords]

bool matchCondType(const L1GtConditionType &, const L1GtConditionType &)

const cms_uint32_t totalTriggerNr() const

get/set total number of L1A sent since start of run

const L1GtfeExtWord gtfeWord() const

get / set GTFE word (record) in the GT readout record

const std::vector< std::vector< int > > & gtPrescaleFactors() const

get the prescale factors by reference

virtual void print(std::ostream &myCout) const

pretty print the content of a L1GtfeWord

virtual void setCurrentFolder(std::string const &fullpath)

const DecisionWordExtended & gtDecisionWordExtended() const

get/set extended algorithms bits (extended decision word)

const cms_uint16_t noAlgo() const

get/set NoAlgo

MonitorElement * m_fdlDataAlgoDecision_NoMatch[TotalBxInEvent][NumberOfGtRecords]

static const int TotalBxInEvent

edm::EDGetTokenT< L1GlobalTriggerReadoutRecord > m_l1GtDataDaqInputToken_

MonitorElement * m_fdlDataTechDecisionMask[TotalBxInEvent][NumberOfGtRecords]

MonitorElement * m_fdlEmulAlgoDecisionUnprescaled[TotalBxInEvent][NumberOfGtRecords]

MonitorElement * m_fdlEmulTechDecision_Err[NumberOfGtRecords]

MonitorElement * m_fdlEmulAlgoDecision[TotalBxInEvent][NumberOfGtRecords]

std::ostringstream m_myCoutStream

const std::vector< L1GtFdlWord > gtFdlVector() const

get the vector of L1GtFdlWord

const cms_uint32_t setupVersion() const

get/set setup version

const std::vector< std::vector< int > > * m_prescaleFactorsTechTrig

T getUntrackedParameter(std::string const &, T const &) const

Log< level::Info, false > LogInfo

virtual void compareDaqRecord(const edm::Event &, const edm::EventSetup &)

L1 GT DAQ record comparison.

std::vector< edm::ParameterSet > m_excludeCondCategTypeObject

MonitorElement * m_fdlEmulAlgoDecisionMask_NoMatch[TotalBxInEvent][NumberOfGtRecords]

MonitorElement * m_fdlDataEmulAlgoDecision_Err[NumberOfGtRecords]

Log< level::Warning, false > LogWarning

const cms_uint16_t bData(int iB) const

get/set B_DATA_CH_IB

const cms_uint16_t bxNr() const

get/set bunch cross number of the actual bx

MonitorElement * m_fdlDataEmul_Err[NumberOfGtRecords]

static const int NumberOfGtRecords

std::vector< L1GtConditionCategory > m_excludedCondCategory

excluded condition categories

const cms_uint16_t recordLength() const

get/set record length for alternative 0

const L1GtPrescaleFactors * m_l1GtPfAlgo

prescale factors

MonitorElement * m_fdlEmulAlgoDecisionPrescaled[TotalBxInEvent][NumberOfGtRecords]

const cms_uint16_t localBxNr() const

get/set local bunch cross number of the actual bx

edm::InputTag m_l1GctDataInputTag

input tag for the L1 GCT hardware record

std::vector< unsigned int > m_triggerMaskAlgoTrig

const cms_uint32_t eventNr() const

get/set event number since last L1 reset generated in FDL

edm::ESGetToken< L1GtTriggerMask, L1GtTriggerMaskAlgoTrigRcd > l1gtTrigmaskAlgoToken_

edm::ESGetToken< L1GtTriggerMenu, L1GtTriggerMenuRcd > l1gtTrigmenuToken_

MonitorElement * m_fdlEmulAlgoDecisionPrescaled_NoMatch[TotalBxInEvent][NumberOfGtRecords]

unsigned long long m_l1GtTmTechCacheID

MonitorElement * m_fdlDataEmulTechDecision_Err[NumberOfGtRecords]

edm::InputTag m_l1GtDataEvmInputTag

input tag for the L1 GT hardware EVM record

const cms_uint16_t boardId() const

get/set board ID

static const unsigned int NumberPhysTriggers

const int bxInEvent() const

get/set bunch cross in the GT event record

MonitorElement * m_fdlDataEmulTechDecisionMask[TotalBxInEvent][NumberOfGtRecords]

void print(std::ostream &myCout) const

pretty print

MonitorElement * m_fdlDataEmulAlgoDecision[TotalBxInEvent][NumberOfGtRecords]

MonitorElement * m_fdlDataAlgoDecisionPrescaledMask_NoMatch[TotalBxInEvent][NumberOfGtRecords]

MonitorElement * m_fdlEmulAlgoDecisionUnprescaled_NoMatch[TotalBxInEvent][NumberOfGtRecords]

const std::vector< L1GtPsbWord > gtPsbVector() const

get the vector of L1GtPsbWord

MonitorElement * m_fdlDataTechDecision[TotalBxInEvent][NumberOfGtRecords]

MonitorElement * m_gtErrorFlag

PSB.

unsigned long long m_l1GtPfTechCacheID

edm::EDGetTokenT< L1GlobalTriggerEvmReadoutRecord > m_l1GtDataEvmInputToken_

const cms_uint32_t eventNr() const

get/set event number since last L1 reset generated in PSB

MonitorElement * m_fdlEmulAlgoDecision_NoMatch[TotalBxInEvent][NumberOfGtRecords]

std::string m_dirName

directory name for L1Extra plots

static const int NumberBData

L1GtObject l1GtObjectStringToEnum(const std::string &)

std::vector< L1GtConditionType > m_excludedCondType

excluded condition types

MonitorElement * m_fdlDataEmulAlgoDecisionUnprescaled[TotalBxInEvent][NumberOfGtRecords]

MonitorElement * m_fdlDataAlgoDecisionMask[TotalBxInEvent][NumberOfGtRecords]

virtual void comparePSB(const edm::Event &, const edm::EventSetup &, const L1GtPsbWord &, const L1GtPsbWord &)

compare the PSB board

const cms_uint16_t bxNr() const

get/set bunch cross number as counted in the GTFE board

const std::vector< unsigned int > & gtTriggerMask() const

get the trigger mask

std::vector< int > m_excludedAlgoList

const std::vector< std::vector< int > > * m_prescaleFactorsAlgoTrig

void printGtDecisionWordExtended(std::ostream &myCout) const

const L1GtfeWord gtfeWord() const

get / set GTFE word (record) in the GT readout record

const L1GtTriggerMask * m_l1GtTmTech

virtual void setBinLabel(int bin, const std::string &label, int axis=1)

set bin label for x, y or z axis (axis=1, 2, 3 respectively)

MonitorElement * m_fdlDataAlgoDecision_Err[NumberOfGtRecords]

MonitorElement * m_fdlDataAlgoDecisionUnprescaledMask_NoMatch[TotalBxInEvent][NumberOfGtRecords]

const DecisionWord & gtDecisionWord() const

get/set/print algorithms bits (decision word)

const cms_uint16_t boardId() const

get/set board ID

const cms_uint16_t bxNr() const

get/set BxNr - bunch cross number of the actual bx

std::vector< int > m_excludeAlgoTrigByBit

exclude algorithm triggers from comparison data - emulator by algorithm bit number

void excludedAlgoList()

exclude from comparison some bits with known disagreement - bit list

bool getData(T &iHolder) const

std::vector< bool > DecisionWord

typedefs

virtual void compareGTFE(const edm::Event &, const edm::EventSetup &, const L1GtfeWord &, const L1GtfeWord &, const int)

compare the GTFE board

MonitorElement * m_fdlDataAlgoDecisionUnprescaled[TotalBxInEvent][NumberOfGtRecords]

bool matchCondCategory(const L1GtConditionCategory &, const L1GtConditionCategory &)

book all histograms for the module

MonitorElement * m_fdlDataAlgoDecisionUnprescaled_NoMatch[TotalBxInEvent][NumberOfGtRecords]

std::vector< bool > DecisionWordExtended

const TechnicalTriggerWord & gtTechnicalTriggerWord() const

get/set technical trigger bits

std::vector< unsigned int > m_triggerMaskTechTrig

const cms_uint16_t recordLength1() const

get/set record length for alternative 1

virtual void compareFDL(const edm::Event &, const edm::EventSetup &, const L1GtFdlWord &, const L1GtFdlWord &, const int)

compare the FDL board

edm::ESGetToken< L1GtPrescaleFactors, L1GtPrescaleFactorsAlgoTrigRcd > l1gtPrescaleAlgoToken_

void printGtTechnicalTriggerWord(std::ostream &myCout) const

MonitorElement * m_fdlDataEmulAlgoDecisionPrescaled[TotalBxInEvent][NumberOfGtRecords]

void print(std::ostream &myCout) const

pretty print the content of a L1GtFdlWord

edm::InputTag m_l1GtEmulDaqInputTag

input tag for the L1 GT emulator DAQ record

const cms_uint16_t localBxNr() const

get/set local bunch cross number of the actual bx

MonitorElement * m_fdlEmulTechDecision[TotalBxInEvent][NumberOfGtRecords]

T getParameter(std::string const &) const

const L1GtPrescaleFactors * m_l1GtPfTech

MonitorElement * m_fdlDataEmulTechDecision[TotalBxInEvent][NumberOfGtRecords]

edm::InputTag m_l1GtEmulEvmInputTag

input tag for the L1 GT emulator EVM record

MonitorElement * m_fdlEmulAlgoDecisionPrescaledMask_NoMatch[TotalBxInEvent][NumberOfGtRecords]

bool excludedAlgo(const int &) const

exclusion status for algorithm with bit i

static const unsigned int NumberTechnicalTriggers

MonitorElement * m_fdlDataAlgoDecision[TotalBxInEvent][NumberOfGtRecords]

bool matchCondL1GtObject(const std::vector< L1GtObject > &, const L1GtObject &)

MonitorElement * m_fdlDataAlgoDecisionPrescaled_NoMatch[TotalBxInEvent][NumberOfGtRecords]

MonitorElement * m_fdlDataEmulAlgoDecisionUnprescaledAllowed[TotalBxInEvent][NumberOfGtRecords]

std::vector< bool > TechnicalTriggerWord

technical trigger bits (64 bits)

const cms_uint16_t finalOR() const

get/set "Final OR" bits

edm::ESGetToken< L1GtTriggerMask, L1GtTriggerMaskTechTrigRcd > l1gtTrigmaskTechToken_

MonitorElement * m_fdlDataAlgoDecisionPrescaled[TotalBxInEvent][NumberOfGtRecords]

const L1GtTriggerMask * m_l1GtTmAlgo

trigger masks

MonitorElement * m_fdlEmulAlgoDecisionMask[TotalBxInEvent][NumberOfGtRecords]

const cms_uint16_t altNrBxBoard() const

get/set alternative for number of BX per board

unsigned long long m_l1GtMenuCacheID

static const int NumberAData

MonitorElement * m_fdlDataTechDecision_Err[NumberOfGtRecords]

edm::EDGetTokenT< L1GlobalTriggerEvmReadoutRecord > m_l1GtEmulEvmInputToken_

const cms_uint16_t boardId() const

get/set board ID

virtual void compareEvmRecord(const edm::Event &, const edm::EventSetup &)

L1 GT EVM record comparison.

const std::vector< L1GtFdlWord > gtFdlVector() const

get the vector of L1GtFdlWord

MonitorElement * book1D(TString const &name, TString const &title, int const nchX, double const lowX, double const highX, FUNC onbooking=NOOP())

std::vector< L1GtObject > m_excludedL1GtObject

excluded L1 GT objects

void printGtDecisionWord(std::ostream &myCout) const

std::vector< std::string > m_excludeAlgoTrigByName

exclude algorithm triggers from comparison data - emulator by algorithm name

unsigned long long m_l1GtPfAlgoCacheID

Protected Member Functions inherited from DQMEDAnalyzer

Protected Member Functions inherited from DQMEDAnalyzer 1.8.16

1.8.16