|

|

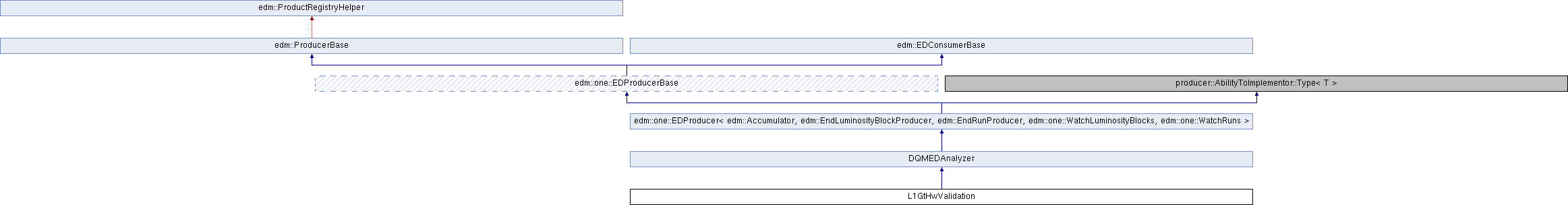

#include <L1GtHwValidation.h>

Protected Member Functions | |

| void | bookHistograms (DQMStore::IBooker &ibooker, const edm::Run &, const edm::EventSetup &) override |

| void | dqmBeginRun (const edm::Run &, const edm::EventSetup &) override |

Protected Member Functions inherited from edm::EDConsumerBase Protected Member Functions inherited from edm::EDConsumerBase | |

| template<typename ProductType , BranchType B = InEvent> | |

| EDGetTokenT< ProductType > | consumes (edm::InputTag const &tag) |

| EDGetToken | consumes (const TypeToGet &id, edm::InputTag const &tag) |

| template<BranchType B> | |

| EDGetToken | consumes (TypeToGet const &id, edm::InputTag const &tag) |

| ConsumesCollector | consumesCollector () |

| Use a ConsumesCollector to gather consumes information from helper functions. More... | |

| template<typename ProductType , BranchType B = InEvent> | |

| void | consumesMany () |

| void | consumesMany (const TypeToGet &id) |

| template<BranchType B> | |

| void | consumesMany (const TypeToGet &id) |

| template<typename ProductType , BranchType B = InEvent> | |

| EDGetTokenT< ProductType > | mayConsume (edm::InputTag const &tag) |

| EDGetToken | mayConsume (const TypeToGet &id, edm::InputTag const &tag) |

| template<BranchType B> | |

| EDGetToken | mayConsume (const TypeToGet &id, edm::InputTag const &tag) |

Private Member Functions | |

| void | analyze (const edm::Event &, const edm::EventSetup &) override |

| virtual void | compareDaqRecord (const edm::Event &, const edm::EventSetup &) |

| L1 GT DAQ record comparison. More... | |

| virtual void | compareEvmRecord (const edm::Event &, const edm::EventSetup &) |

| L1 GT EVM record comparison. More... | |

| virtual void | compareFDL (const edm::Event &, const edm::EventSetup &, const L1GtFdlWord &, const L1GtFdlWord &, const int) |

| compare the FDL board More... | |

| virtual void | compareGt_Gct (const edm::Event &, const edm::EventSetup &) |

| virtual void | compareGTFE (const edm::Event &, const edm::EventSetup &, const L1GtfeWord &, const L1GtfeWord &, const int) |

| compare the GTFE board More... | |

| virtual void | comparePSB (const edm::Event &, const edm::EventSetup &, const L1GtPsbWord &, const L1GtPsbWord &) |

| compare the PSB board More... | |

| virtual void | compareTCS (const edm::Event &, const edm::EventSetup &, const L1TcsWord &, const L1TcsWord &) |

| compare the TCS board More... | |

| bool | excludedAlgo (const int &) const |

| exclusion status for algorithm with bit i More... | |

| void | excludedAlgoList () |

| exclude from comparison some bits with known disagreement - bit list More... | |

| bool | matchCondCategory (const L1GtConditionCategory &, const L1GtConditionCategory &) |

| book all histograms for the module More... | |

| bool | matchCondL1GtObject (const std::vector< L1GtObject > &, const L1GtObject &) |

| bool | matchCondType (const L1GtConditionType &, const L1GtConditionType &) |

Static Private Attributes | |

| static const int | NumberOfGtRecords = 2 |

| static const int | TotalBxInEvent = 5 |

Additional Inherited Members | |

Public Types inherited from edm::one::EDProducerBase Public Types inherited from edm::one::EDProducerBase | |

| typedef EDProducerBase | ModuleType |

Public Types inherited from edm::ProducerBase Public Types inherited from edm::ProducerBase | |

| using | ModuleToResolverIndicies = std::unordered_multimap< std::string, std::tuple< edm::TypeID const *, const char *, edm::ProductResolverIndex >> |

| typedef ProductRegistryHelper::TypeLabelList | TypeLabelList |

Public Types inherited from edm::EDConsumerBase Public Types inherited from edm::EDConsumerBase | |

| typedef ProductLabels | Labels |

Static Public Member Functions inherited from edm::one::EDProducerBase Static Public Member Functions inherited from edm::one::EDProducerBase | |

| static const std::string & | baseType () |

| static void | fillDescriptions (ConfigurationDescriptions &descriptions) |

| static void | prevalidate (ConfigurationDescriptions &descriptions) |

Protected Attributes inherited from DQMEDAnalyzer Protected Attributes inherited from DQMEDAnalyzer | |

| edm::EDPutTokenT< DQMToken > | lumiToken_ |

| edm::EDPutTokenT< DQMToken > | runToken_ |

Description: compare hardware records with emulator records for L1 GT records.

Implementation: Get the L1 GT records from data and from emulator. Compare every board between data and emulator.

$Date$

Description: compare hardware records with emulator records for L1 GT records.

Implementation: Get the L1 GT records from data and from emulator. Compare every board between data and emulator.

Definition at line 56 of file L1GtHwValidation.h.

|

explicit |

Definition at line 52 of file L1GtHwValidation.cc.

References CondNull, edm::ParameterSet::getParameter(), l1GtConditionCategoryStringToEnum(), l1GtConditionTypeStringToEnum(), l1GtObjectStringToEnum(), LogDebug, m_excludeCondCategTypeObject, m_excludedCondCategory, m_excludedCondType, m_excludedL1GtObject, m_l1GctDataInputTag, m_l1GtDataDaqInputTag, m_l1GtDataDaqInputToken_, m_l1GtDataEvmInputTag, m_l1GtDataEvmInputToken_, m_l1GtEmulDaqInputTag, m_l1GtEmulDaqInputToken_, m_l1GtEmulEvmInputTag, m_l1GtEmulEvmInputToken_, ObjNull, AlCaHLTBitMon_QueryRunRegistry::string, and TypeNull.

|

override |

Definition at line 155 of file L1GtHwValidation.cc.

|

overrideprivate |

Definition at line 2245 of file L1GtHwValidation.cc.

References compareDaqRecord(), compareEvmRecord(), compareGt_Gct(), m_nrEvJob, and m_nrEvRun.

|

overrideprotected |

Definition at line 165 of file L1GtHwValidation.cc.

References DQMStore::IBooker::book1D(), excludedAlgoList(), edm::EventSetup::get(), L1GtTriggerMenu::gtAlgorithmMap(), L1GtPrescaleFactors::gtPrescaleFactors(), L1GtTriggerMask::gtTriggerMask(), L1GtTriggerMenu::gtTriggerMenuImplementation(), LogDebug, m_dirName, m_excludedAlgoList, m_excludedAlgorithmsAgreement, m_fdlDataAlgoDecision, m_fdlDataAlgoDecision_Err, m_fdlDataAlgoDecision_NoMatch, m_fdlDataAlgoDecisionMask, m_fdlDataAlgoDecisionMask_NoMatch, m_fdlDataAlgoDecisionPrescaled, m_fdlDataAlgoDecisionPrescaled_NoMatch, m_fdlDataAlgoDecisionPrescaledMask_NoMatch, m_fdlDataAlgoDecisionUnprescaled, m_fdlDataAlgoDecisionUnprescaled_NoMatch, m_fdlDataAlgoDecisionUnprescaledMask_NoMatch, m_fdlDataEmul, m_fdlDataEmul_Err, m_fdlDataEmulAlgoDecision, m_fdlDataEmulAlgoDecision_Err, m_fdlDataEmulAlgoDecisionMask, m_fdlDataEmulAlgoDecisionPrescaled, m_fdlDataEmulAlgoDecisionUnprescaled, m_fdlDataEmulAlgoDecisionUnprescaledAllowed, m_fdlDataEmulTechDecision, m_fdlDataEmulTechDecision_Err, m_fdlDataEmulTechDecisionMask, m_fdlDataTechDecision, m_fdlDataTechDecision_Err, m_fdlDataTechDecisionMask, m_fdlEmulAlgoDecision, m_fdlEmulAlgoDecision_Err, m_fdlEmulAlgoDecision_NoMatch, m_fdlEmulAlgoDecisionMask, m_fdlEmulAlgoDecisionMask_NoMatch, m_fdlEmulAlgoDecisionPrescaled, m_fdlEmulAlgoDecisionPrescaled_NoMatch, m_fdlEmulAlgoDecisionPrescaledMask_NoMatch, m_fdlEmulAlgoDecisionUnprescaled, m_fdlEmulAlgoDecisionUnprescaled_NoMatch, m_fdlEmulAlgoDecisionUnprescaledMask_NoMatch, m_fdlEmulTechDecision, m_fdlEmulTechDecision_Err, m_fdlEmulTechDecisionMask, m_gtErrorFlag, m_gtfeDataEmul, m_l1GtMenu, m_l1GtMenuCacheID, m_l1GtPfAlgo, m_l1GtPfAlgoCacheID, m_l1GtPfTech, m_l1GtPfTechCacheID, m_l1GtTmAlgo, m_l1GtTmAlgoCacheID, m_l1GtTmTech, m_l1GtTmTechCacheID, m_nrEvRun, m_prescaleFactorsAlgoTrig, m_prescaleFactorsTechTrig, m_triggerMaskAlgoTrig, m_triggerMaskTechTrig, NumberOfGtRecords, L1GlobalTriggerReadoutSetup::NumberPhysTriggers, L1GlobalTriggerReadoutSetup::NumberTechnicalTriggers, edm::ESHandle< T >::product(), MonitorElement::setBinLabel(), DQMStore::IBooker::setCurrentFolder(), str, AlCaHLTBitMon_QueryRunRegistry::string, and TotalBxInEvent.

|

privatevirtual |

L1 GT DAQ record comparison.

Definition at line 1979 of file L1GtHwValidation.cc.

References L1GtPsbWord::boardId(), L1GtPsbWord::bxInEvent(), compareFDL(), compareGTFE(), comparePSB(), TauDecayModes::dec, MonitorElement::Fill(), edm::Event::getByToken(), L1GlobalTriggerReadoutRecord::gtFdlVector(), L1GlobalTriggerReadoutRecord::gtfeWord(), L1GlobalTriggerReadoutRecord::gtPsbVector(), edm::HandleBase::isValid(), LogDebug, m_agree, m_dataOnly, m_dataOnlyMask, m_emulOnly, m_emulOnlyMask, m_gtErrorFlag, m_l1GtDataDaqInputToken_, m_l1GtEmulDaqInputToken_, m_myCoutStream, m_nrDataEventError, and m_nrEmulEventError.

Referenced by analyze().

|

privatevirtual |

L1 GT EVM record comparison.

Definition at line 2147 of file L1GtHwValidation.cc.

References compareFDL(), compareGTFE(), edm::Event::getByToken(), L1GlobalTriggerEvmReadoutRecord::gtFdlVector(), L1GlobalTriggerEvmReadoutRecord::gtfeWord(), edm::HandleBase::isValid(), LogDebug, m_l1GtDataEvmInputToken_, m_l1GtEmulEvmInputToken_, m_myCoutStream, m_nrDataEventError, and m_nrEmulEventError.

Referenced by analyze().

|

privatevirtual |

compare the FDL board

Definition at line 1030 of file L1GtHwValidation.cc.

References L1GtFdlWord::boardId(), L1GtFdlWord::bxInEvent(), L1GtFdlWord::bxNr(), TauDecayModes::dec, L1GtFdlWord::eventNr(), excludedAlgo(), MonitorElement::Fill(), L1GtFdlWord::finalOR(), L1GtFdlWord::gtDecisionWord(), L1GtFdlWord::gtDecisionWordExtended(), L1GtFdlWord::gtPrescaleFactorIndexAlgo(), L1GtFdlWord::gtTechnicalTriggerWord(), L1GtFdlWord::localBxNr(), LogDebug, LogTrace, m_agree, m_dataOnly, m_dataOnlyMask, m_emulOnly, m_emulOnlyMask, m_excludedAlgorithmsAgreement, m_fdlDataAlgoDecision, m_fdlDataAlgoDecision_Err, m_fdlDataAlgoDecision_NoMatch, m_fdlDataAlgoDecisionMask, m_fdlDataAlgoDecisionMask_NoMatch, m_fdlDataAlgoDecisionPrescaled, m_fdlDataAlgoDecisionPrescaled_NoMatch, m_fdlDataAlgoDecisionPrescaledMask_NoMatch, m_fdlDataAlgoDecisionUnprescaled, m_fdlDataAlgoDecisionUnprescaled_NoMatch, m_fdlDataAlgoDecisionUnprescaledMask_NoMatch, m_fdlDataEmul, m_fdlDataEmul_Err, m_fdlDataEmulAlgoDecision, m_fdlDataEmulAlgoDecision_Err, m_fdlDataEmulAlgoDecisionMask, m_fdlDataEmulAlgoDecisionPrescaled, m_fdlDataEmulAlgoDecisionUnprescaled, m_fdlDataEmulAlgoDecisionUnprescaledAllowed, m_fdlDataEmulTechDecision, m_fdlDataEmulTechDecision_Err, m_fdlDataEmulTechDecisionMask, m_fdlDataTechDecision, m_fdlDataTechDecision_Err, m_fdlDataTechDecisionMask, m_fdlEmulAlgoDecision, m_fdlEmulAlgoDecision_Err, m_fdlEmulAlgoDecision_NoMatch, m_fdlEmulAlgoDecisionMask, m_fdlEmulAlgoDecisionMask_NoMatch, m_fdlEmulAlgoDecisionPrescaled_NoMatch, m_fdlEmulAlgoDecisionPrescaledMask_NoMatch, m_fdlEmulAlgoDecisionUnprescaled_NoMatch, m_fdlEmulAlgoDecisionUnprescaledMask_NoMatch, m_fdlEmulTechDecision, m_fdlEmulTechDecision_Err, m_fdlEmulTechDecisionMask, m_myCoutStream, m_triggerMaskAlgoTrig, m_triggerMaskTechTrig, L1GtFdlWord::noAlgo(), nanoDQM_cff::prescaleFactor, L1GtFdlWord::print(), L1GtFdlWord::printGtDecisionWord(), L1GtFdlWord::printGtDecisionWordExtended(), L1GtFdlWord::printGtTechnicalTriggerWord(), AlCaHLTBitMon_QueryRunRegistry::string, and TotalBxInEvent.

Referenced by compareDaqRecord(), and compareEvmRecord().

|

privatevirtual |

compare the GCT collections obtained from L1 GT PSB with the input GCT collections

Definition at line 2237 of file L1GtHwValidation.cc.

Referenced by analyze().

|

privatevirtual |

compare the GTFE board

get record length for alternative 1

get record length for alternative 0

get bunch cross number as counted in the GTFE board

get setup version

get boards contributing to EVM respectively DAQ record

alternative for number of BX per board correlated with active boards bit value is 0: take alternative 0 bit value is 1: take alternative 1

get total number of L1A sent since start of run

Definition at line 823 of file L1GtHwValidation.cc.

References L1GtfeWord::activeBoards(), L1GtfeWord::altNrBxBoard(), L1GtfeWord::boardId(), L1GtfeWord::bxNr(), TauDecayModes::dec, MonitorElement::Fill(), LogDebug, m_gtfeDataEmul, m_myCoutStream, L1GtfeWord::print(), L1GtfeWord::recordLength(), L1GtfeWord::recordLength1(), L1GtfeWord::setupVersion(), AlCaHLTBitMon_QueryRunRegistry::string, and L1GtfeWord::totalTriggerNr().

Referenced by compareDaqRecord(), and compareEvmRecord().

|

privatevirtual |

compare the PSB board

get/set A_DATA_CH_IA

get/set B_DATA_CH_IB

Definition at line 1792 of file L1GtHwValidation.cc.

References L1GtPsbWord::aData(), L1GtPsbWord::bData(), L1GtPsbWord::boardId(), L1GtPsbWord::bxInEvent(), L1GtPsbWord::bxNr(), TauDecayModes::dec, L1GtPsbWord::eventNr(), L1GtPsbWord::localBxNr(), LogDebug, m_myCoutStream, L1GtPsbWord::NumberAData, L1GtPsbWord::NumberBData, and L1GtPsbWord::print().

Referenced by compareDaqRecord().

|

privatevirtual |

compare the TCS board

Definition at line 1973 of file L1GtHwValidation.cc.

|

overrideprotected |

Definition at line 161 of file L1GtHwValidation.cc.

|

private |

exclusion status for algorithm with bit i

Definition at line 2481 of file L1GtHwValidation.cc.

References m_excludedAlgoList.

Referenced by compareFDL().

|

private |

exclude from comparison some bits with known disagreement - bit list

Definition at line 2326 of file L1GtHwValidation.cc.

References L1GtTriggerMenu::gtAlgorithmMap(), L1GtTriggerMenu::gtConditionMap(), l1GtConditionCategoryEnumToString(), l1GtConditionTypeEnumToString(), l1GtObjectEnumToString(), LogTrace, m_excludeAlgoTrigByBit, m_excludeAlgoTrigByName, m_excludedAlgoList, m_excludedCondCategory, m_excludedCondType, m_excludedL1GtObject, m_l1GtMenu, matchCondCategory(), matchCondL1GtObject(), matchCondType(), electrons_cff::objType, and AlCaHLTBitMon_QueryRunRegistry::string.

Referenced by bookHistograms().

|

private |

book all histograms for the module

return true if an algorithm has a condition of that category for CondNull, it returns always true

Definition at line 2263 of file L1GtHwValidation.cc.

References CondNull.

Referenced by excludedAlgoList().

|

private |

return true if an algorithm has a condition containing that object for ObjNull, it returns always true

Definition at line 2298 of file L1GtHwValidation.cc.

References ObjNull.

Referenced by excludedAlgoList().

|

private |

return true if an algorithm has a condition of that type for TypeNull, it returns always true

Definition at line 2281 of file L1GtHwValidation.cc.

References TypeNull.

Referenced by excludedAlgoList().

|

private |

internal members

Definition at line 199 of file L1GtHwValidation.h.

Referenced by compareDaqRecord(), and compareFDL().

|

private |

Definition at line 200 of file L1GtHwValidation.h.

Referenced by compareDaqRecord(), and compareFDL().

|

private |

Definition at line 202 of file L1GtHwValidation.h.

Referenced by compareDaqRecord(), and compareFDL().

|

private |

directory name for L1Extra plots

Definition at line 137 of file L1GtHwValidation.h.

Referenced by bookHistograms().

|

private |

Definition at line 201 of file L1GtHwValidation.h.

Referenced by compareDaqRecord(), and compareFDL().

|

private |

Definition at line 203 of file L1GtHwValidation.h.

Referenced by compareDaqRecord(), and compareFDL().

|

private |

exclude algorithm triggers from comparison data - emulator by algorithm bit number

Definition at line 147 of file L1GtHwValidation.h.

Referenced by excludedAlgoList().

|

private |

exclude algorithm triggers from comparison data - emulator by algorithm name

Definition at line 144 of file L1GtHwValidation.h.

Referenced by excludedAlgoList().

|

private |

exclude algorithm triggers from comparison data - emulator by condition category and / or type

Definition at line 141 of file L1GtHwValidation.h.

Referenced by L1GtHwValidation().

|

private |

Definition at line 279 of file L1GtHwValidation.h.

Referenced by bookHistograms(), excludedAlgo(), and excludedAlgoList().

|

private |

Definition at line 264 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

excluded condition categories

Definition at line 153 of file L1GtHwValidation.h.

Referenced by excludedAlgoList(), and L1GtHwValidation().

|

private |

excluded condition types

Definition at line 156 of file L1GtHwValidation.h.

Referenced by excludedAlgoList(), and L1GtHwValidation().

|

private |

excluded L1 GT objects

Definition at line 159 of file L1GtHwValidation.h.

Referenced by excludedAlgoList(), and L1GtHwValidation().

|

private |

Definition at line 218 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 228 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 222 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 221 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 225 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 219 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 223 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 226 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 220 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 224 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 227 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

FDL (0 for DAQ, 1 for EVM record)

Definition at line 216 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 249 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 243 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 248 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 247 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 244 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 245 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 246 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 260 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 262 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 261 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 252 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 254 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 253 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 230 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 240 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 234 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 233 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 237 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 231 of file L1GtHwValidation.h.

Referenced by bookHistograms().

|

private |

Definition at line 235 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 238 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 232 of file L1GtHwValidation.h.

Referenced by bookHistograms().

|

private |

Definition at line 236 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 239 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 256 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 258 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 257 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

PSB.

ErrorFlag a la HardwareValidation

Definition at line 271 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareDaqRecord().

|

private |

histograms

GTFE

Definition at line 213 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareGTFE().

|

private |

input tag for the L1 GCT hardware record

Definition at line 134 of file L1GtHwValidation.h.

Referenced by L1GtHwValidation().

|

private |

input tag for the L1 GT hardware DAQ record

Definition at line 122 of file L1GtHwValidation.h.

Referenced by L1GtHwValidation().

|

private |

Definition at line 282 of file L1GtHwValidation.h.

Referenced by compareDaqRecord(), and L1GtHwValidation().

|

private |

input tag for the L1 GT hardware EVM record

Definition at line 125 of file L1GtHwValidation.h.

Referenced by L1GtHwValidation().

|

private |

Definition at line 284 of file L1GtHwValidation.h.

Referenced by compareEvmRecord(), and L1GtHwValidation().

|

private |

input tag for the L1 GT emulator DAQ record

Definition at line 128 of file L1GtHwValidation.h.

Referenced by L1GtHwValidation().

|

private |

Definition at line 283 of file L1GtHwValidation.h.

Referenced by compareDaqRecord(), and L1GtHwValidation().

|

private |

input tag for the L1 GT emulator EVM record

Definition at line 131 of file L1GtHwValidation.h.

Referenced by L1GtHwValidation().

|

private |

Definition at line 285 of file L1GtHwValidation.h.

Referenced by compareEvmRecord(), and L1GtHwValidation().

|

private |

trigger menu

Definition at line 172 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and excludedAlgoList().

|

private |

Definition at line 173 of file L1GtHwValidation.h.

Referenced by bookHistograms().

|

private |

|

private |

Definition at line 177 of file L1GtHwValidation.h.

Referenced by bookHistograms().

|

private |

Definition at line 179 of file L1GtHwValidation.h.

Referenced by bookHistograms().

|

private |

Definition at line 180 of file L1GtHwValidation.h.

Referenced by bookHistograms().

|

private |

|

private |

Definition at line 187 of file L1GtHwValidation.h.

Referenced by bookHistograms().

|

private |

Definition at line 189 of file L1GtHwValidation.h.

Referenced by bookHistograms().

|

private |

Definition at line 190 of file L1GtHwValidation.h.

Referenced by bookHistograms().

|

private |

an output stream to print into it can then be directed to whatever log level is desired

Definition at line 163 of file L1GtHwValidation.h.

Referenced by compareDaqRecord(), compareEvmRecord(), compareFDL(), compareGTFE(), and comparePSB().

|

private |

counters

Definition at line 166 of file L1GtHwValidation.h.

Referenced by compareDaqRecord(), and compareEvmRecord().

|

private |

Definition at line 167 of file L1GtHwValidation.h.

Referenced by compareDaqRecord(), and compareEvmRecord().

|

private |

Definition at line 275 of file L1GtHwValidation.h.

Referenced by analyze().

|

private |

Definition at line 276 of file L1GtHwValidation.h.

Referenced by analyze(), and bookHistograms().

|

private |

Definition at line 182 of file L1GtHwValidation.h.

Referenced by bookHistograms().

|

private |

Definition at line 183 of file L1GtHwValidation.h.

Referenced by bookHistograms().

|

private |

Definition at line 192 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

private |

Definition at line 193 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

|

staticprivate |

Definition at line 208 of file L1GtHwValidation.h.

Referenced by bookHistograms().

|

staticprivate |

Definition at line 207 of file L1GtHwValidation.h.

Referenced by bookHistograms(), and compareFDL().

1.8.11

1.8.11